NDK Configuration 配置指南¶

1. SDK Config 系统简介¶

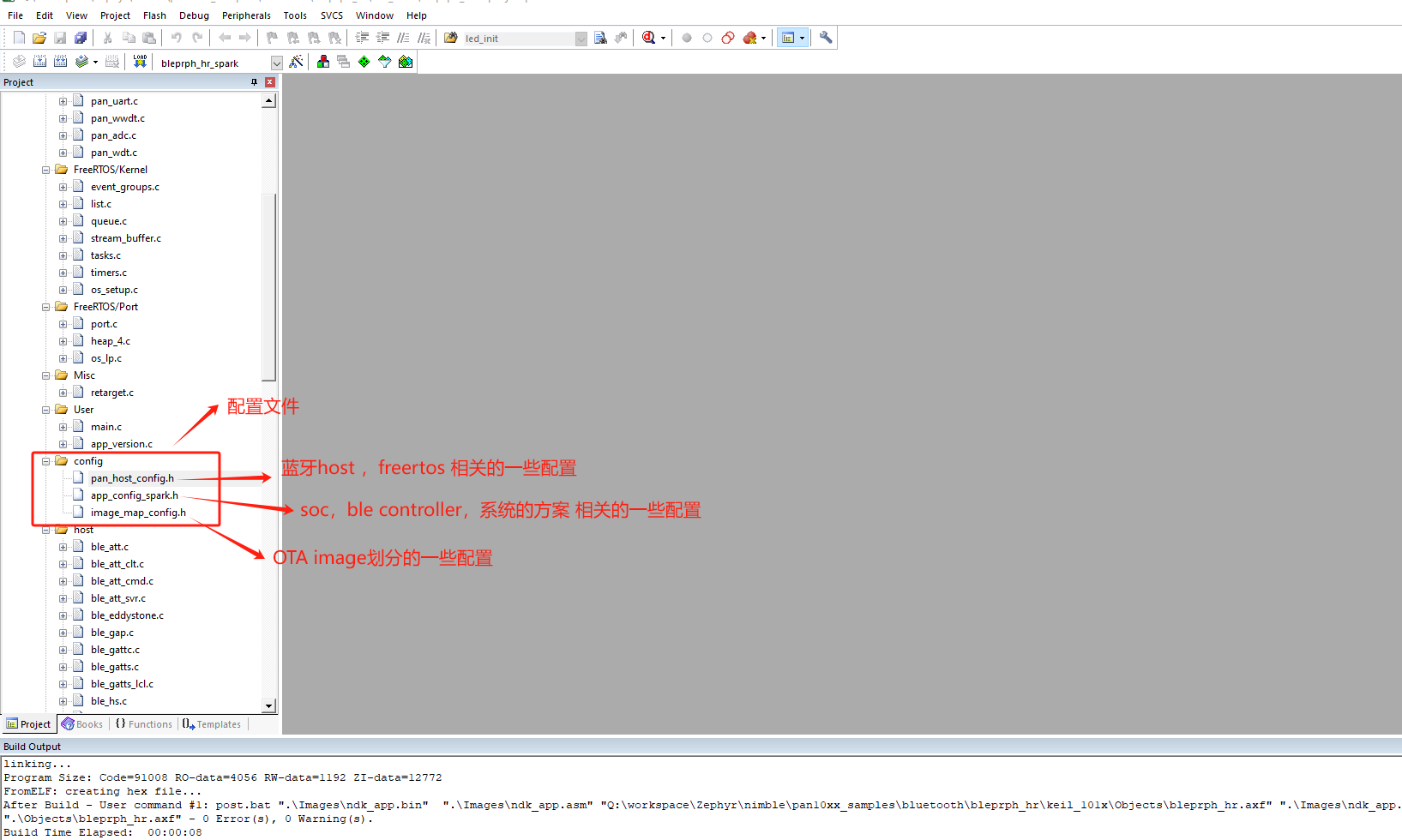

NDK 中设计了一套 SDK 配置系统,其面向用户的接口是一个名为 sdk_config.h的头文件,位于各个 App 工程目录内。结合 Keil MDK 的 Configuration Wizard 功能,用户可以方便地通过图形菜单的方式修改 SDK 中提供的各个配置。

2. SDK Config 配置说明¶

目前 SDK Config 配置共分为 8 大类,依次为 Application Config、 Component Config、Platform Config、LowPower Enable、RTOS Enable、BLE Enable 、Flash/Image Config、Log/Debug Config。

SDK Config Overview¶

注:其中第一个类别

Application Config,是为用户预留的菜单,用户可在自己的 App 中自定义一些 Config 配置,并将其放在 SDK Config 的Application Config配置菜单下以方便后续使用。

2.1 Component Config¶

Component Config 是与系统组件相关的配置,目前支持 Config 配置的组件有 SFUD、FatFs 以及 CherryUSB 等三个。

2.1.1 SFUD 组件¶

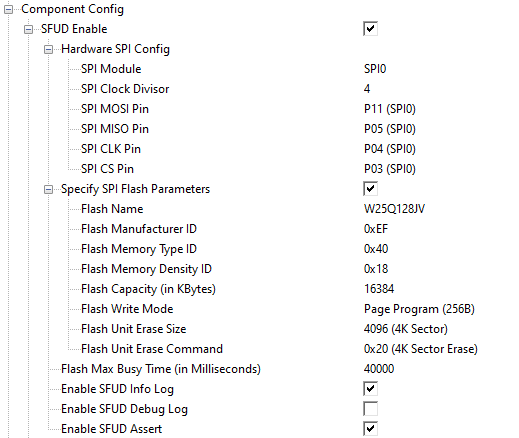

SFUD Component Configuration¶

SFUD Enable:使能 SFUD (Serial Flash Universal Driver) 组件

Hardware SPI Config:指定 SoC 硬件 SPI 相关配置

SPI Module:SPI 模块选择(PAN10xx SoC 支持 2 个硬件 SPI:SPI0/SPI1)

SPI Clock Divisor:SPI 时钟分频因子(spi_clk_div,支持 2 ~ 512 之间的偶数分频),实际 SPI 时钟速率为 clk_spi = clk_apb / spi_clk_div = clk_sys / apb_clk_div / spi_clk_div;例如当前 SFUD 使用 SPI0 模块(其挂载在 APB1 总线上),且 SPI Clock Divisor 选择 4 分频,而在 Platform Config 配置中,系统时钟 System Clock 选择 32MHz,APB1 Clock Divisor 选择 2 分频,那么实际 SPI0 时钟速率为 clk_spi = clk_sys / apb_clk_div / spi_clk_div = 32MHz / 2 / 4 = 4MHz

SPI MOSI Pin:SPI MOSI 引脚选择(注意 SPI0 与 SPI1 支持的引脚各不相同,选择的时候需与 SPI Module 配置保持一致)

SPI MISO Pin:SPI MISO 引脚选择(注意 SPI0 与 SPI1 支持的引脚各不相同,选择的时候需与 SPI Module 配置保持一致)

SPI CLK Pin:SPI Clock 引脚选择(注意 SPI0 与 SPI1 支持的引脚各不相同,选择的时候需与 SPI Module 配置保持一致)

SPI CS Pin:SPI CS 引脚选择(注意 SPI0 与 SPI1 支持的引脚各不相同,选择的时候需与 SPI Module 配置保持一致)

Specify SPI Flash Parameters:勾选后可手动指定外部 SPI Flash 相关参数(否则使用

sfud_falsh_def.h文件 SFUD_FLASH_CHIP_TABLE 列表中默认支持的 Flash 参数)Flash Name:指定 SPI Flash 的字符串名称,SFUD 初始化成功后会将其打印出来

Flash Manufacturer ID:指定 SPI Flash 厂商 ID,其是 Flash JDID(JEDEC ID)的组成部分,具体需查阅 SPI Flash Datasheet

Flash Memory Type ID:指定 SPI Flash 存储器类型 ID,其是 Flash JDID(JEDEC ID)的组成部分,具体需查阅 SPI Flash Datasheet

Flash Memory Density ID:指定 SPI Flash 存储器容量 ID,其是 Flash JDID(JEDEC ID)的组成部分,具体可查阅 SPI Flash Datasheet,也可通过计算得出,方法是对当前 Flash 的容量(字节)取以 2 为底的对数,例如 Flash 大小为 16MB,则其 Memory Density ID 为

mem_density_id=log2(16*1024*1024)=24,亦可反推 2^24 = 16MBFlash Capacity:指定 SPI Flash 的容量(单位为 KBytes),例如 16MB 的 Flash,则填写 16384,程序中会使用此值与 Flash Memory Density ID 进行交叉验算,若二者不一致则会编译报错

Flash Write Mode:指定 SPI Flash 写模式,当前仅支持 256 字节的 Page Program(几乎所有 SPI Flash 均支持此模式)

Flash Unit Erase Size:指定 SPI Flash 最小擦除大小,当前仅支持 4096 字节的 4KB Sector Erase(几乎所有 SPI Flash 均支持此大小)

Flash Unit Erase Command:指定 SPI Flash 最小擦除大小对应的擦除命令,4KB Sector Erase 对应的命令为 0x20(几乎所有 SPI Flash 均支持此命令)

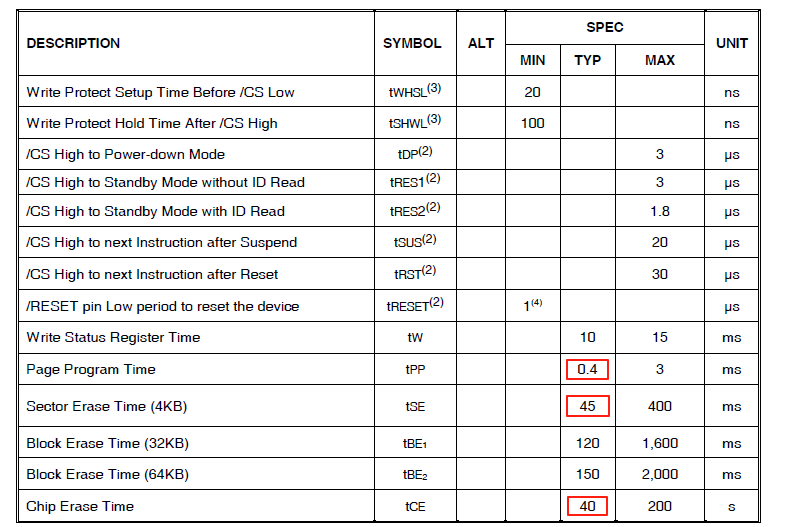

Flash Max Busy Time:指定 Flash(擦/写)Busy 状态最大超时等待时间(单位为 ms);SPI Flash 擦写数据的过程一般耗时较久(至少为毫秒级),而 SFUD 组件的 Flash 操作接口均为 Polling 方式,其会等待 Flash 操作完成后返回,因此需要设置一个合理的超时时间,以防止 Flash 操作过程中出现死等的情况;实际项目中,此超时时间需要配置成 Flash 所有擦/写操作所需的最大时间(

max_busy_time = max(tPP, tSE, tCE)),此时间可通过查阅 Flash Datasheet 中的 AC Electrical Characteristics 章节获取;例如,PAN10xx EVB 底板上默认的 SPI Flash 型号为 W25Q128JV,通过查阅 Datasheet 可知其擦写 Typical 时间 tPP = 0.4ms、tSE = 45ms、tCE = 40000ms,因此这里我们将 Flash Max Busy Time 配置为它们中的最大值 40000

AC Electrical Characteristics of W25Q128JV Flash¶

Enable SFUD Info Log:使能 SFUD 组件 Info 级别的日志输出;注意此功能还受 Log/Debug Config - Enable Log 配置开关控制

Enable SFUD Debug Log:使能 SFUD 组件 Debug 级别的日志输出,建议仅在调试问题的过程中使能,默认不使能;注意此功能还受 Log/Debug Config - Enable Log 配置开关控制

Enable SFUD Assert:使能 SFUD 组件内部 Assert 断言功能,若 Enable SFUD Debug Log 也处于使能状态,则 Assert 触发的时候还会输出 Log;注意此功能还受 Log/Debug Config - Enable Assert 配置开关控制

2.1.2 FatFs 组件¶

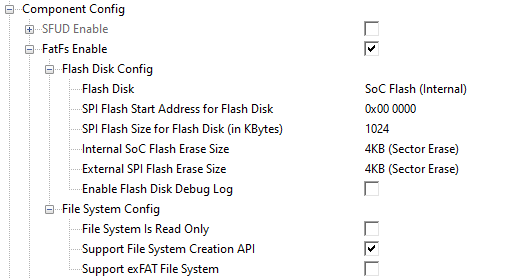

FatFs Component Configuration¶

FatFs Enable:使能 FatFs 组件

Flash Disk Config:FatFs 后端 Flash 存储器(Flash Disk)相关配置

Flash Disk:指定 FatFs 使用的 Flash,可选择内部 SoC Flash 或外部 SPI FLash

若选择 SoC Flash,则 FatFs 使用 SoC 内部 Flash 的 User Custom Partition 分区,其大小可通过 Flash/Image Config : Flash Partition Config : Uaer Custom Flash Partition Size 配置修改

若选择 SPI Flash,则 FatFs 使用外部 SPI Flash(通过 SFUD 组件访问,因此还需使能 SFUD 组件)

SPI Flash Start Address for Flash Disk:指定 FatFs 使用的外部 SPI Flash 的起始地址(仅当 Flash Disk 配置选择外部 SPI Flash 时有效)

SPI Flash Size for Flash Disk:指定 FatFs 使用的外部 SPI Flash 的大小(单位为 KBytes)(仅当 Flash Disk 配置选择外部 SPI Flash 时有效)

Internal SoC Flash Erase Size:指定内部 SoC FLash 最小擦除单元大小,默认选择 4KB (Sector Erase),此配置比较通用;某些 PAN10xx 型号还支持 256B (Page Erase),选择此选项可缩小 DiskIO Driver 内部使用的缓存 HEAP,节约 SRAM 空间(仅当 Flash Disk 配置选择内部 SoC Flash 时有效)

External SPI Flash Erase Size:指定外部 SPI FLash 最小擦除单元大小,默认选择 4KB (Sector Erase),此配置比较通用;某些 SPI Flash 型号还支持 256B (Page Erase),选择此选项可缩小 DiskIO Driver 内部使用的缓存 HEAP,节约 SRAM 空间(仅当 Flash Disk 配置选择外部 SPI Flash 时有效)

Enable Flash Disk Debug Log:使能 FatFs 组件的 Log 日志输出,建议仅在调试问题的过程中使能,默认不使能;注意此功能还受 Log/Debug Config - Enable Log 配置开关控制

File System Config:FatFs 文件系统相关配置

File System Is Read Only:将 FatFs 文件系统配置为只读,即禁用所有写操作相关的 API 接口:

f_write()、f_sync()、f_unlink()、f_mkdir()、f_chmod()、f_rename()、f_truncate()、f_getfree()等Support File System Creation API:允许创建并初始化文件系统,即使能文件系统创建接口

f_mkfs()Support exFAT File System:支持 exFAT 文件系统格式

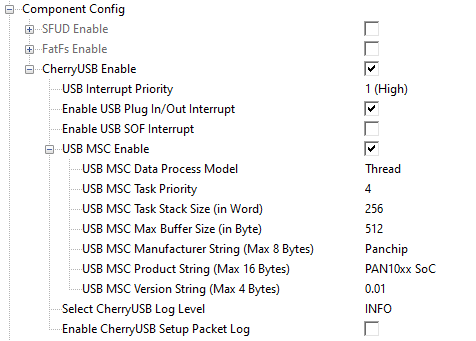

2.1.3 CherryUSB 组件¶

CherryUSB Component Configuration¶

CherryUSB Enable:使能 CherryUSB 组件

USB Interrupt Priority:指定 USB 中断优先级

Enable USB Plug In/Out Interrupt:使能 USB 硬件插入/拔出中断

Enable USB SOF Interrupt:使能 USB 硬件 SOF (Start Of Frame) 中断

USB MSC Enable:使能 USB 大容量存储(Mass Storage Class, MSC)功能

USB MSC Data Process Model:指定 USB MSC 的数据处理方式,可选择 Thread 线程模式或者 Polling 查询模式:

若选择 Thread 线程模式,则 CherryUSB MSC 模块内部会创建一个用于数据处理的 OS 任务(USB MSC Task),因此要求 OS(RTOS Enable)也需使能

若选择 Polling 查询模式,则可以不依赖于 RTOS,但需在程序主循环中及时调用

usbd_msc_polling()接口进行 USB MSC 数据处理

USB MSC Task Priority:指定 USB MSC Task 的任务优先级(仅当 USB MSC Data Process Model 配置选择外部 Thread 时有效)

USB MSC Task Stack Size:指定 USB MSC Task 的任务栈大小,单位为 Word(仅当 USB MSC Data Process Model 配置选择外部 Thread 时有效)

USB MSC Max Buffer Size:指定 USB MSC 内部 Buffer 大小,单位为 Byte;其默认值为 512,无特殊情况请勿更改此值

USB MSC Manufacturer String:为 USB MSC 设备指定 Manufacturer String,最大 8 字节

USB MSC Product String:为 USB MSC 设备指定 Product String,最大 16 字节

USB MSC Version String:为 USB MSC 设备指定 Version String,最大 4 字节

Select CherryUSB Log Level:选择 CherryUSB 组件内部 Log 等级;注意此功能还受 Log/Debug Config - Enable Log 配置开关控制

Enable CherryUSB Setup Packet Log:使能 USB Setup Packet 包交互过程 Log,默认关闭,一般仅调试过程中可以开启;注意此功能还受 Log/Debug Config - Enable Log 配置开关控制

2.2 Platform Config¶

Platform Config 是与芯片平台相关的配置,包括时钟、电源、平台相关的特殊 Feature 等项目:

SoC Platform Configuration¶

Chip Power Mode:选择芯片的供电模式

SDK 中的例程大部分都是默认选择 DCDC 模式,用户也可根据项目需要切换至 LDO 模式

芯片在 DCDC 模式下动态功耗更低,但需要板级硬件电路的支持(BUCK外围电路)

System Clock:配置系统高速时钟频率

SDK 例程中,PAN107x 工程配置一般是默认选择 32MHz (DPLL),PAN101x 工程配置一般是默认选择 48MHz (DPLL)

APB1 Clock Divisor:配置 APB1 时钟分频系数

芯片 APB1 上的外设有:I2C、SPI0、UART0、PWM、ADC、WDT、WWDT、TIMER0

SDK 中的例程一般是默认选择 2 分频,用户也可根据项目需要改变此分频值

实际项目中,若某些 APB1 上的外设需要工作在较高的速度下(如 SPI0),可能默认的 2 分频无法满足需要,那么可将 APB1 改为不分频(No Divider)

实际项目中,若对芯片的动态功耗有要求,但是对 APB1 上的外设速度要求不高,那么可将 APB1 分频改为能正常工作的最大值(需通过试验得出),以降低芯片动态功耗

APB2 Clock Divisor:配置 APB2 时钟分频系数

芯片 APB2 上的外设有:SPI1、UART1、TIMER1、TIMER2、CLKTRIM

SDK 中的例程一般是默认选择 2 分频,用户也可根据项目需要改变此分频值

实际项目中,若某些 APB2 上的外设需要工作在较高的速度下(如 SPI1),可能默认的 2 分频无法满足需要,那么可将 APB2 改为不分频(No Divider)

实际项目中,若对芯片的动态功耗有要求,但是对 APB2 上的外设速度要求不高,那么可将 APB2 分频改为能正常工作的最大值(需通过试验得出),以降低芯片动态功耗

32K Low-Speed Clock Source:配置系统低速时钟源

选择 RCL,芯片无需外接 32K 晶振,但精度相对较低(低功耗蓝牙应用的功耗会稍高一些)

选择 XTL,芯片需要外接 32K 晶振(32768 Hz),精度更高(低功耗蓝牙应用的功耗会更低一些)

选择 ACT32K,蓝牙内部 32K 定时器将使用高速晶振(32M XTH)分频后的时钟源,精度高,但此时仅支持蓝牙非低功耗的场景,一般是主机或者多连接的场景

Force Calib RCL Clock:选择是否在系统初始化的时候强制校准一次 RCL 时钟

若前面低速时钟源选择 RCL,则此处强烈建议勾选强制校准 RCL 时钟,否则 RCL 不准确可能会影响 APP 定时相关的功能

注意此配置使能后,后续

soc_api.c中 32K 时钟的相关接口也会使用此处实际校准值,而不是预设的理想值(RCL:32000)

Measure Actual 32K Clock:可选择在系统初始化阶段强制测量一次当前 32K 时钟的实际频率(可以是 XTL 或 RCL),这样后续

soc_api.c中 32K 时钟的相关接口就会使用实际测量值,而不是预设的理想值(XTL:32768,RCL:32000)Enable RAM Function:将一些对时间敏感的函数编译到 SRAM 中执行,加快程序执行速度,以达到降低功耗的效果(程序执行得更快,可以让芯片有更多时间处于进入低功耗模式)

此配置使能后,代码中带有

CONFIG_RAM_CODE前缀的函数将被编译到 SRAM 中执行,其中包括关键的 OS 调度函数、OS DeepSleep 低功耗处理函数、蓝牙中断服务函数等SDK 例程中,PAN107x 工程配置会默认使能此选项(PAN107x SRAM 有 48KB,相对充足),而 PAN101x 工程配置则默认不使能此选项以节省 SRAM 空间(PAN101x SRAM 仅有 16KB)

Enable Flash LDO:使能内部专用的 1.8v Flash LDO 给 Flash 供电

芯片上电默认 Flash 供电电源为芯片 VBAT,当使能此选项后,Flash 供电电源将切换至内部 1.8v Flash LDO,以达到降低 Flash 功耗的效果

SDK 例程中,此选项默认都是使能的,一般无需修改此默认配置

Remap Vector Table to SRAM:将中断向量表映射到 SRAM 中的指定地址,以加快中断响应速度

使能此配置会多占用 256 Bytes 的 SRAM 空间

SDK 例程中,PAN107x 工程配置会默认使能此选项,而 PAN101x 工程配置则默认不使能此选项以节省 SRAM 空间

Interrupt Stack Size:指定中断 ISR 栈(MSP)大小,单位为字节

C Library Heap Size:指定 Keil C Library (Microlib) 自带 Heap 大小,单位为字节,默认配置为 0 表示不使能此功能,其他值表示使能此功能;当使能此功能后,可使用 C Library 自带的 Heap 相关接口,如

malloc()、free()等若使能了 OS,则推荐使用 OS 提供的 Heap 接口(如

pvPortMalloc()、vPortFree()等),而不是 C Library 中自带的接口。Enable Auto Power Optimization:定时检测当前芯片温度,并根据温度自动优化芯片的电源配置(目前使用两个温度临界点(0℃、50℃)将温度分为三个区间)

通过子配置 Temperature Sample Interval 可以更改定时温度检测的时间间隔

使能子配置 Enable DVDD Voltage Optimization 后,常温下芯片数字电路的供电电源 DVDD 电压会由 1.16v 降至 1.12v 左右(实际产品中不建议使能此配置)

此功能通过芯片 ADC 模块读取芯片内部温度传感器数据,这个流程本身也会增加芯片动态功耗(5 分钟时间间隔配置下芯片平均电流约增加 200nA)

Enable LVR (Low Voltage Reset):使能 SoC 硬件低压复位模块,芯片将在 VBAT 引脚电压低于 1.85v 后进入复位状态,直到 VBAT 电压重新抬高到 1.85v 以上

通过子配置 LVR Debounce Time 可以选择 LVR 电压去抖时间(共 6 个档位)

通过子配置 Disable LVR in LowPower Mode 可以在系统进入 DeepSleep/Standby 的时候关闭 LVR 功能以节约功耗(LVR 模块本身耗电约 500nA)

Enable BOD (Brown-Out Detect):使能 SoC 硬件电压监测模块,支持芯片在 VBAT 引脚低于指定电压的时候复位或者产生中断

通过子配置 BOD Mode 指定 BOD 模式,可选择 Reset 复位模式或者 Interrupt 中断模式:

若选择 Reset 复位模式,芯片将会在 VBAT 引脚电压降低到配置的 Falling 电压之后进入复位状态,直到 VBAT 电压重新抬高到配置的 Rising 电压以上

若选择 Interrupt 中断模式,芯片将会分别在 VBAT 引脚电压降低到配置的 Falling 电压时和 VBAT 引脚电压抬高到配置的 Rising 电压时产生中断,SDK 中默认的中断行为是直接打印 Log,用户可在 App 中重新实现

BOD_IRQHandlerOverlay()函数,以满足特定的需求(代码可参考soc.c中的默认实现)

通过子配置 BOD Trigger Voltage 指定 BOD 触发电压,共 7 个档位可供选择

通过子配置 BOD Debounce Time 可以选择 BOD 电压去抖时间(共 6 个档位)

通过子配置 Disable BOD in LowPower Mode 可以在系统进入 DeepSleep/Standby 的时候关闭 BOD 功能以节约功耗(BOD 模块本身耗电约 500nA)

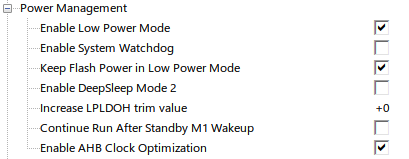

2.3 LowPower Enable¶

LowPower Enable 是与芯片低功耗相关的配置,包括低功耗使能、低功耗下的相关电源配置等项目:

LowPower Configuration¶

Low Power Enable:使能系统低功耗流程及低功耗相关的 API 接口

若同时使能了 OS,则芯片会在 OS Ilde Task 中自动进入 DeepSleep 低功耗模式

使能此配置后,可以通过调用

soc_enter_standby_mode_1()和soc_enter_standby_mode_0()两个接口使芯片分别进入 Standby M1 和 Standby M0 两种低功耗模式

Enable System Watchdog:使能系统 Watchdog 功能

Keep Flash Power in Low Power Mode:芯片 DeepSleep 状态下,Flash 不断电,而是切换至 DP 低功耗状态

Select DeepSleep Mode:选择 DeepSleep Power 模式

若选择 Mode 1,则芯片进入 DeepSleep 状态后使用 Power Mode 1,此模式下芯片内部数字电路通过 0.5v LPLDOL 和 0.7v LPLDOH 这两个 LDO 配合供电,支持的唤醒源为 All GPIOs、SleepTimer CH0/CH1/CH2,常温下芯片低功耗底电流约 3~4 uA

若选择 Mode 2,则芯片进入 DeepSleep 状态后使用 Power Mode 2,此模式下芯片内部数字电路均通过 0.7v LPLDOH 供电,支持的唤醒源为 All GPIOs、SleepTimer CH0/CH1/CH2、HW APB Timer0/1/2、常温下芯片低功耗底电流约 6~7 uA;另外此低功耗模式下还支持 PWM 输出(底电流会更大)

DeepSleep Entering Delay Timer at Boot Stage:指定系统初始化完成后多少毫秒内不允许 OS 进入 DeepSLeep 低功耗状态,时间设置为 0 则可以禁用此功能;使能此配置可防止 SDK 例程启动后过快进入低功耗状态而导致 JLink 断连(导致不好通过 JLink 烧录程序),实际项目中可以根据需要选择是否关闭此功能

Increase LPLDOH trim value:抬高 LPLDOH 电压档位(档位步进约 50mV)

芯片 LPLDOH 电压值在校准后约为 700mV,但某些应用场景下可能需要抬高 LPLDOH 电压值

Continue Run After Standby M1 Wakeup:芯片从低功耗 Standby M1 模式醒来后,CPU 接着从睡眠前的代码位置继续运行而不是复位

使能此配置后,芯片唤醒后 CPU 虽然没有复位,但芯片除 GPIO 外的所有外设状态都是复位的,因此醒来后需要重新配置使用到的外设模块

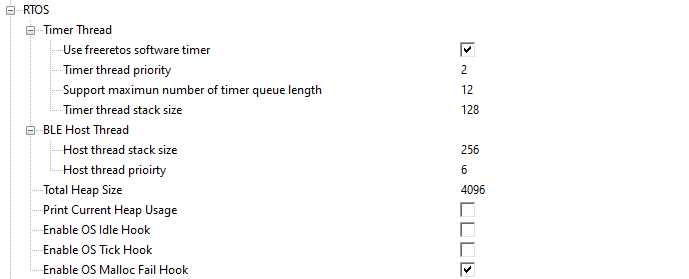

2.4 RTOS Enable¶

RTOS Enable 是与 OS 相关的配置,NDK 中的大部分应用均以 FreeRTOS 为基础进行构建,且 NimBLE 必须依赖 FreeRTOS 运行:

RTOS Configuration¶

RTOS Enable:系统中使能 FreeRTOS

The Maximum Number of OS Task:设置 OS Task 的最大优先级

OS Total Heap Size:设置 OS Heap 大小,单位为 Byte

OS Heap 主要由下面这些对象消耗的,一般无需关心细节,可勾选 Enable OS Malloc Fail Hook 功能进行 Heap 余量检测,若不够则会打印 Malloc Failed Log,方案中可通过此方法自行调整大小,默认的工程一般都是稍有余量。

Total Heap

unit

IDLE Thread STACK

size*4

Timer Thread STACK

size*4

BLE Host Thread STACK

size*4

OS 相关的对象的使用,例如实例化定时器的个数,信号量的个数

\

BLE ATT GATT entry 等,一般服务越多,支持的角色,就需要的越多

\

BLE Host buffer,Host 使用的部分 buf,也是占用 Total heap size

\

OS Main Thread Stack Size:设置 Main Task 栈大小,单位为 Word

OS Main Thread Priority:设置 Main Task 任务优先级(值越大,任务优先级越高)

OS BLE Host Thread Stack Size:设置 BLE Host Task 栈大小,单位为 Word

场景

任务栈大小推荐值

备注

不支持配对加密

256 - 300 words

实际的栈大小还和用户的操作有关系

支持配对加密

400 - 500 words

实际的栈大小还和用户的操作有关系

OS BLE Host Thread Priority:设置 BLE Host Task 任务优先级(值越大,任务优先级越高)

OS Timer Task Enable:使能 OS Timer Task(软件定时器)

OS Timer Task Stack Size:设置 Timer Task 栈大小,单位为 Word

OS Timer Task Priority:设置 Timer Task 任务优先级(值越大,任务优先级越高)

The Maximun Number of OS Timer Queue Length:设置 OS Timer 支持的最大队列(Queue)长度,一般一个定时操作需要 4-5 个 Queue,详情参考 FreeRTOS 官方文档

Enable OS Idle Hook:使能 OS 调度进入 Idle Task 后给予用户的回调函数

Enable OS Tick Hook:使能 OS 调度进入 Tick 更新后给予用户的回调函数

Enable OS Malloc Fail Hook:使能 OS Malloc 内存失败后给予用户的回调函数

Enable OS Stack OverFlow Hook:使能 OS Task Stack 栈溢出检测功能,详情参考 FreeRTOS 官方文档

OS Log: Print Current Heap Usage:使能 Malloc 的 Log,在调用

pvPortMalloc()函数的时候打印 Heap 申请和使用信息

2.5 BLE Enable¶

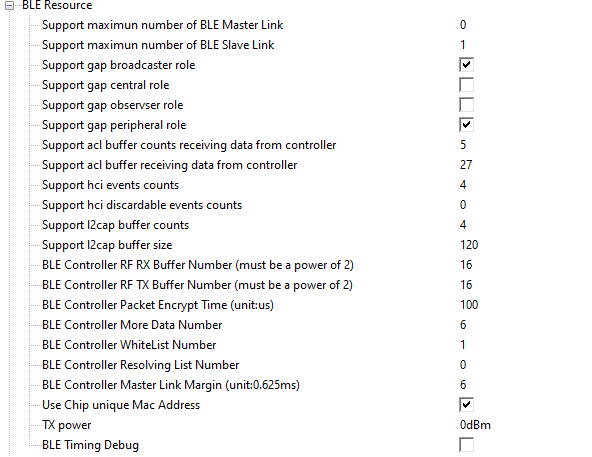

2.5.1 BLE Resource¶

BLE Resource Configuration¶

Use Chip unique Mac Address

使用芯片的出厂的 mac 地址

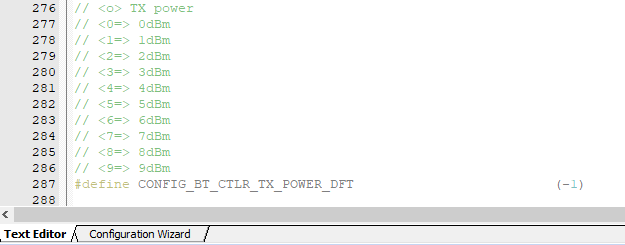

RF TX power

支持范围是 -40 到 9dBm,最小步长是 1dBm,如果需要设置 0 以下,可以通过 text Editor修改.

Tx Power Configuration¶

Support maximun number of BLE Master Link

设置 ble controller 支持的 master links 数量,如果设置为0,表示不支持 master link。用户可以设置任意数量的 master link 数,具体可以设置多少个由RAM和Flash资源以及搜索连接的算法决定。

多个master link 建立连接以后,ble controller 能保证连接之间不冲突,且各个连接具有相同的或者不同的数据带宽(用户可配)。

Support maximun number of BLE Slave Link

设置 ble controller 支持的 slave links 数量, 如果设置为0,表示不支持 slave link。用户可以设置任意数量的 slave link 数,但是建议 slave link 数最多设置 4 个,原因如下:

slave link 数设置越多,消耗资源越多

slave link 数设置越多,建立连接以后,连接之间的冲突会很频繁,导致数据有较大延时;当冲突严重时,可能导致断连。

GAP 角色定义

Support GAP broadcaster role

Support GAP central role

Support GAP observer role

Support GAP peripheral role

Host Buffer 相关

BLE Host Max ATT MTU Size

设置ATT MTU Size,它决定了用户数据的大小,这个值必须 >= 23B。

BLE Host HCI Rx ACL buffer size 和 BLE Host HCI Rx ACL buffer counts

Host Rx ACL buffer用于 host 接收 controller 上报的 ACL data 的 buffer.

BLE Host HCI Rx ACL buffer size用于设置ACL buffer size, 其取值范围是27B - 251B, 如果使用LE Secure Connection, 则ACL buffer至少设置65B。BLE Host HCI Rx ACL buffer counts用于设置ACL buffer个数ACL buffer的设置必须保证至少能接收2个 ATT MTU Size的数据。

Host 没有Tx ACL buffer可以设置,因为Host 下发的 ACL data 直达 Controller, Tx ACL buffer在controller实现。

BLE Host HCI events counts

Host HCI event counts用于设置 Host 接收controller 上报的HCI event(除adv report event 外) buffer的个数, HCI event buffer size不需要用户设置,协议栈已经按照spec要求配置好了

Host HCI event counts应该根据实际情况配置,如果交互数据比较频繁或者多连接,建议HCI Event buffer Count >= 8, buffer少了将出现异常,Buffer 不够时会有log输出。

BLE Host HCI discardable events counts BLE Host HCI discardable events counts用于设置Host 接收 controller 上报的Adv report event buffer的个数,Host HCI discardable events buffer size 不需要用户设置,协议栈已经按照spec要求配置好了。

BLE Host L2CAP buffer size 和 BLE Host L2CAP buffer counts

L2CAP buffer用于蓝牙数据发送,包括SMP和ATT

L2CAP buffer是基于内存池技术实现的链式 buffer, 例如:假如用户配置L2CAP buffer参数是120B/4个,用户有240B的数据需要发送,那么协议栈首先申请一个120B的buffer,存储120B的用户数据,然后再申请120B的buffer,用于存取剩余的120B的用户数据,最后将这两个buffer通过链表连接为一个整体。

BLE Controller 相关

BLE Controller RF Rx buffer 和 BLE Controller RF Rx Buffer Number

RF Rx buffer 用于 controller 接收 peer 设备数据的 buffer, RF Rx buffer使用的是MAC层专用的一块RAM,在 pan107 上这个专用的 RAM 有 8KB,实际 BLE Controller 只能使用7.5KB。(RF Tx/Rx 共用 7.5kB专用RAM)

RF Rx buffer Size 由 Host HCI Rx ACL buffer size 决定

RF Rx buffer Number 需要配置,且 Number 只能是2的 n 次幂, 例如:2,4,8,16,32…

对于single connection的应用来说,RF Rx buffer 设置为 8 即可

对于multi connection的应用来说,由于 multi connection 共用 Rx buffer,所以需要确保平均每个connection 至少有1 - 2个Rx buffer可用。如果Rx buffer设置少了,当controller一直没有Rx buffer可用时,数据将一直重传,可能导致 peer 上层协议数据交互超时而主动断连。

BLE Controller RF Tx buffer 和 BLE Controller RF Tx Buffer Number

RF Tx buffer 用于controller发送数据的buffer, RF Tx buffer使用的是MAC层专用的RAM,在pan107上这个专用的RAM有8KB,实际BLE Controller 只能使用7.5KB.

(RF Tx/Rx 共用 7.5kB专用RAM)RF Tx buffer Size 由 Host HCI Rx ACL buffer size 决定

RF Tx buffer Number需要配置,且Number只能是2的 n 次幂, 例如:2,4,8,16,32…

对于single connection的应用来说,RF Tx buffer 设置为 4或者8 即可

对于multi connection的应用来说,multi connection中的每个connection的Tx buffer是各自独立的,因此设置越大, 消耗的MAC专用RAM越多,但是能保证多个connection具有同等的数据带宽,使多个connection具有极好的数据吞吐率。

BLE Controller Packet Encrypt Time

如果支持配对建议写到 300us,否则写 100us

BLE Controller More Data Number

用于配置一个connection interval发送包的最大个数, range: 1-6

BLE Controller WhiteList Number

用于配置白名单个数,根据实际情况设置,默认是 1

BLE Controller Resolving List Number

用于配置可解析列表的个数(目前尚不支持该功能)

BLE Controller Master Link Margin

用于设置多master connection之前的间隔, 用于多连接以调节connection数据带宽。

BLE 中断优先级相关

BLE LL IRQ priority

用于配置 BLE LL 中断优先级,默认 BLE LL 中断优先级是最高的。

如果用户的中断需要较高的优先级,且用户的中断执行时间足够短 ,例如 < 30us 时,可以将BLE LL中断优先级调低一档。

BLE Event Handler IRQ priority

用于配置 BLE Event Handler 中断优先级,默认 BLE Event Handler 中断优先级为 次高优先级。

如果用户中断需要较高优先级,可以调低 BLE Event Handler 中断优先级

需要注意 BLE Event Handler 主要处理 Controller 上报的 Event 和 ACL 到 host, 以及处理 Host下发的 HCI Cmd 和 ACL,如果中断优先级变低,则处理变的缓慢,对于实时性或者数据率要求高的应用慎用。

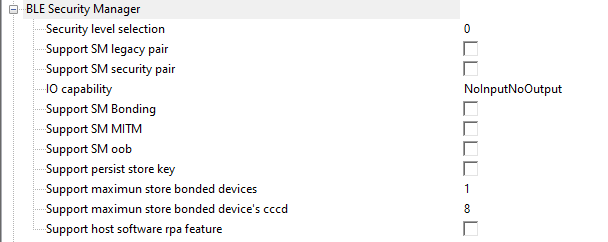

2.5.2 BLE Security Manager¶

BLE Security Manager Configuration¶

Select Security Level

用于设置应用最低安全级别,注意如果peer设备的安全级别小于这里设置的安全级别,协议栈为了安全将拒接对端数据交互。

Enable SM Legacy Pair 和 Enable SM Security Pair

用于Enable/Disable BLE Legacy Pair和 BLE Secure Connection

Select IO Capability

用于设置本地设备的 IO 能力

Enable SM Bonding / Enable MITM / Enable SM OOB

用于设置本地设备的认证能力

Support persist store key

用于使能pair信息存储功能,pair信息将常驻在flash上

Support maximun store bonded devices

用于设置支持的最大 bonding 数目,这个数目越大需要的 Key-Value-Store 的区域也越大

Support maximun store bonded device’s cccd

用于设置支持的最大bonding 设备的 cccd,根据实现项目来

Support host software rpa feature

用于使能 Host RPA 功能,建议一直开着

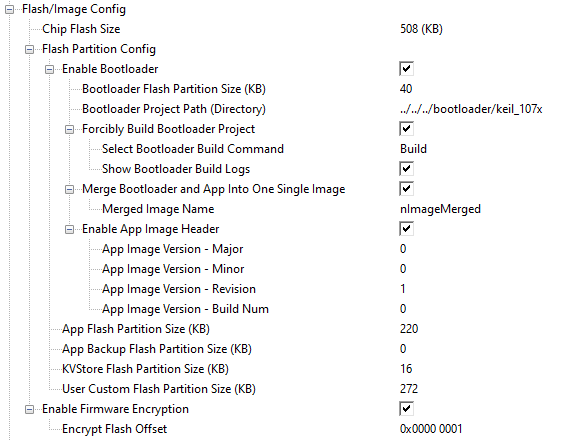

2.6 Flash/Image Config¶

Flash/Image Config 主要包括芯片 Flash 分区规划及特殊 Image 生成相关的配置:

Flash/Image Configuration¶

2.6.1 Chip Flash Size¶

指定当前芯片的 Flash 大小,需与实际使用的芯片 Flash 大小保持一致。

目前 PAN107x 芯片的 Flash 大小均为 512KB(其中尾部 4KB 为保留区域,存放芯片出厂校准信息,因此用户可用的实际空间为 508KB)

目前 PAN101x 芯片的 Flash 大小均为 256KB(其中尾部 4KB 为保留区域,存放芯片出厂校准信息,因此用户可用的实际空间为 252KB)

2.6.2 Flash Partition Config¶

Flash Partition Config 用于配置与 Flash 分区强相关的功能,如 Flash 各个分区的大小、是否使能 Bootloader等。

Enable Bootloader:使能 Bootloader

Bootloader Flash Partition Size:指定 Bootloader 分区大小(KB)

Bootloader Project Path (Directory):指定 Bootloader Keil 工程路径,可以是绝对路径或者相对路径,注意路径分隔符应使用斜杠

/,而不是反斜杠\Forcibly Build Bootloader Project:在当前 App 工程的 Post Build 阶段强制编译一次 Bootloader 工程

通过子配置 Select Bootloader Build Command 可指定编译命令,可选择 Build 增量编译或 Rebuild 重新编译

通过子配置 Show Bootloader Build Logs 可以在当前 App 工程的编译输出 Log 界面中显示 Bootloader 的编译 Log

Merge Bootloader and App Into One Single Image:使能后,在当前 App 工程的 Post Build 阶段,会先将 Bootloader Image 拷贝到当前 App 工程的 Images 目录下,然后将其与当前 App Image 合并生成新的 Image

通过子配置 Merged Image Name 可以指定合并后 Image 的名称,默认为 nImageMerged

Enable App Image Header:使能 Image Header,即为 App 添加一个 512 字节大小的 Image Header

使能 App Image Header 后,可以通过子配置项指定当前 Image 的版本号信息

注意目前 SDK 框架下,若使能了 Bootloader,则必须同时使能 App Image Header,因为 SDK 中 DFU/OTA 组件均依赖 Image Header

App Flash Partition Size:设置当前 App Flash 分区大小(KB)

若未使能 Bootloader,则 App Flash 分区起始地址为 0;若使能了 Bootloader,则 App Flash 分区地址为紧挨着 Bootloader 分区的地址,默认 Bootloader 分区大小为 40KB,因此 App Flash 分区起始地址为 0xA000

根据项目需要修改即可(必须配置为非 0 值才有意义)

App Backup Flash Partition Size:设置 App Backup Flash 分区(App 备份区)大小(KB)

是否使用 App 备份区需根据实际情况选择:例如当应用需要使用蓝牙 OTA 功能时,则必须使用 App 备份区,并且此区域大小应与 App 区保持一致,同时需使能 Bootloader;其他情况则可以不使用 App 备份区

KVStore Flash Partition Size:设置 KVStore Flash 分区大小(KB)

当应用中不使用 KVStore 组件时,可将此项配置为 0x0

当应用中需使用 KVStore 组件时,需将此项配置为 8(KB)的整数倍

注意 KVStore 内部实现是存在交换区的,并且每个键值对占用的最小 Flash 空间为 256 字节,因此项目中应该根据实际需要去估计 KVStore 分区的大小,详见 Flash KVStore 例程 文档

User Custom Flash Partition Size:设置 User Custom 用户自定义 Flash 分区大小(KB)

当应用中不使用 User Custom 用户自定义分区时,可将此项配置为 0x0

当应用中需使用 User Custom 用户自定义分区时,需将此项配置为非 0 值(注意不要超出 Flash 大小,否则会弹出预编译报错提醒)

2.6.3 Enable Firmware Encryption¶

Enable Firmware Encryption 用于配置是否使能 App Image 加密特性。

此功能需配合 Image 加密脚本(

encrypt_info.yaml)使用,详情参考 FW Encryption 例程。

当使能 Firmware Encryption 配置后,可以通过配置项 Encrypt Flash Offset 指定 Flash 的加密位置:

这里 1 个 offset 表示 1 个 Flash Page(256 字节),例如若希望加密 Flash 0x1000 ~ 0x10FF 地址区间,则需将 Encrypt Flash Offset 配置为 16

2.7 Log/Debug Config¶

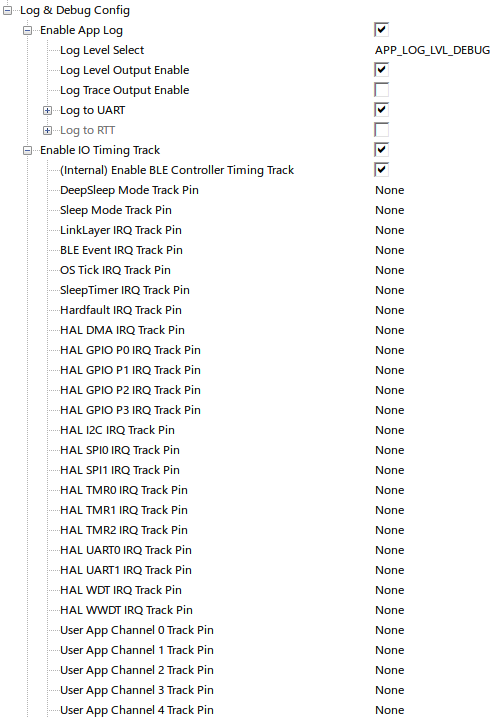

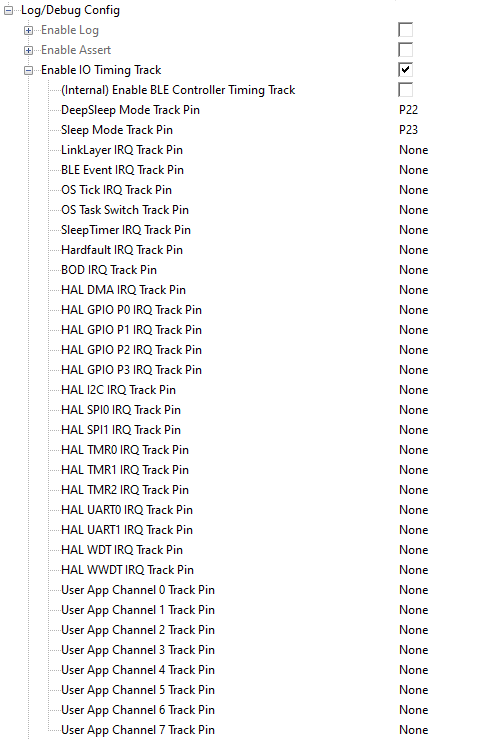

Log/Debug Config 是与 Log 日志和 Debug 调试相关的配置:

Log/Debug Configuration¶

2.7.1 Enable Log¶

Enable Log:使能 Log 日志打印功能

Enable APP Log:使能 App Log 相关功能与接口,用于 App 工程中的 Log 打印

通过子配置 Select Log Level 可以选择当前 Log 输出等级

通过子配置 Print Log Level String 可以选择是否打印 Log 等级前缀

通过子配置 Print Log Verbose String 可以选择是否打印 Log 所处的源码文件、行数、函数等信息

Enable SYS Log:使能 SYS Log 相关功能与接口,用于 SDK 底层的 Log 打印

通过子配置 Select Log Level 可以选择当前 Log 输出等级

通过子配置 Print Log Level String 可以选择是否打印 Log 等级前缀

通过子配置 Print Log Verbose String 可以选择是否打印 Log 所处的源码行数等信息

Log Output to UART:将 Log 输出至 UART 串口,可配置 UART Tx 引脚和波特率

通过子配置 Log UART Tx Pin 可以配置 Log UART Tx 引脚

通过子配置 Log UART Baudrate 可以配置 Log UART 波特率

Log Output to RTT:将 Log 输出至 Segger RTT,可配置 RTT Buffer 大小

通过子配置 RTT Log Buffer Size 可以配置 RTT Buffer 大小

APP Log Backend:选择 APP Log 的后端实现,推荐选择

printk以减少代码大小和任务栈消耗只有在需要打印浮点数的时候才建议选择

printf

SYS Log Backend:选择 SYS Log 的后端实现,推荐选择

printk以减少代码大小和任务栈消耗只有在需要打印浮点数的时候才建议选择

printf

BLE Controller Log Backend:选择 BLE Controller Lib 中 Log 的后端实现,推荐选择

vprintk以减少代码大小和任务栈消耗只有在需要打印浮点数的时候才建议选择

vprintf

2.7.2 Enable Assert¶

Enable Assert:使能 Assert 断言功能

Enable APP Assert:使能 App 代码中的 Assert 断言

Enable SYS Assert:使能 SDK 底层的 Assert 断言

2.7.3 Enable IO Timing Track¶

Enable IO Timing Track 用于配置是否使能 App Track 组件,当使能 App Track 组件后,可以通过一些子项修改相关配置。

IO Timing Track Configuration¶

(Internal) Enable BLE Controller Timing Track:使能蓝牙 Controller 内部事件的 Timing Track

注意:无特殊需要请勿勾选此项,否则可能会影响 App 正常 IO 功能

… Track Pin:配置各模块的 Timing Track IO 引脚,其中:

以 “HAL” 开头的是 HAL Driver 预设的 GPIO Track 信号

以 “User” 开头的是用户可在 App 使用的 GPIO Track 信号

剩下的是一些重要系统流程中预设的 GPIO Track 信号

若相应的 GPIO 信号设置为 “None”,则表示 Disable 该信号,程序中不会编译相关 Code

注意:所有预设的(非 User 开头)Track Pin 中,除了 DeepSleep Mode Track Pin 和 Sleep Mode Track Pin 是低电平表示进入低功耗状态,高电平表示退出低功耗状态外,其他所有 Track Pin 均为高电平表示进入当前流程,低电平表示退出当前流程

2.7.4 Mux Clocks to IO Pads¶

Mux Clocks to IO Pads 用于将一些内部时钟信号 Mux 到 IO 引脚上,一般用于调试或一些特殊应用场景中。

Mux 32K Low-Speed Clock to P11:将内部 32K 时钟 Mux 到 P11 引脚上

Mux AHB (System) Clock to P06:将内部系统时钟(AHB)Mux 到 P06 引脚上

Mux 32M RCH Clock to P17:将内部 32MHz RCH 时钟 Mux 到 P17 引脚上

Mux 32M XTH Clock to P27:将 32MHz XTH 时钟 Mux 到 P27 引脚上

Mux DPLL Clock (divided by 8) to P23:将内部 DPLL 时钟 8 分频后 Mux 到 P23 引脚上

2.7.5 Enable Startup Long Delay¶

在系统初始化的早期阶段,插入一段长时间的延时(约 1s),以满足某些调试需求。

例如在一个使能了 DeepSleep 低功耗的蓝牙应用中,系统会频繁进出低功耗,这会导致 SWD/Jlink 烧录变得困难(低功耗状态下由于电压原因,SWD 是无法正常工作的),影响调试效率,那么此时就可以使能这个长延时配置,JLink 在多次尝试 SWD 通信均不成功的时候,会拉一下芯片 Reset 引脚复位芯片,那么在复位后的系统初始化阶段大概率 JLink 就可以正常识别 SWD 并进入烧录或调试流程了。