量产烧录¶

1 芯片烧录口硬件连接¶

对于遵循 PAN271x 硬件参考设计 文档规范的方案硬件板,可支持通过 SWD 接口烧录程序。

a)芯片支持通过 JLink 或 Panlink 两种方式进行烧录,其接线方式分别如表1-1、表1-2所示。

JLink |

连接 |

PAN271x SoC |

|---|---|---|

VTref 3.3V |

<—> |

VBAT |

6.5V |

<—> |

P22 |

GND |

<—> |

GND |

SWDIO |

<—> |

P01 |

SWDCLK |

<—> |

P00 |

注:6.5V 为外接高压电源,提供烧录 PAN271x 芯片 OTP 用。需要单独电路提供。

Panlink 2.0 |

连接 |

PAN271x SoC |

|---|---|---|

VDD |

<—> |

VBAT |

(6V) |

<—> |

P22 |

GND |

<—> |

GND |

A3 |

<—> |

P01 |

A4 |

<—> |

P00 |

注:(6V) PAN-LINK 的 6.5V 高压输出,提供烧录 PAN271x 芯片 OTP 用。默认不输出,只有在执行烧录时才会自动控制输出。

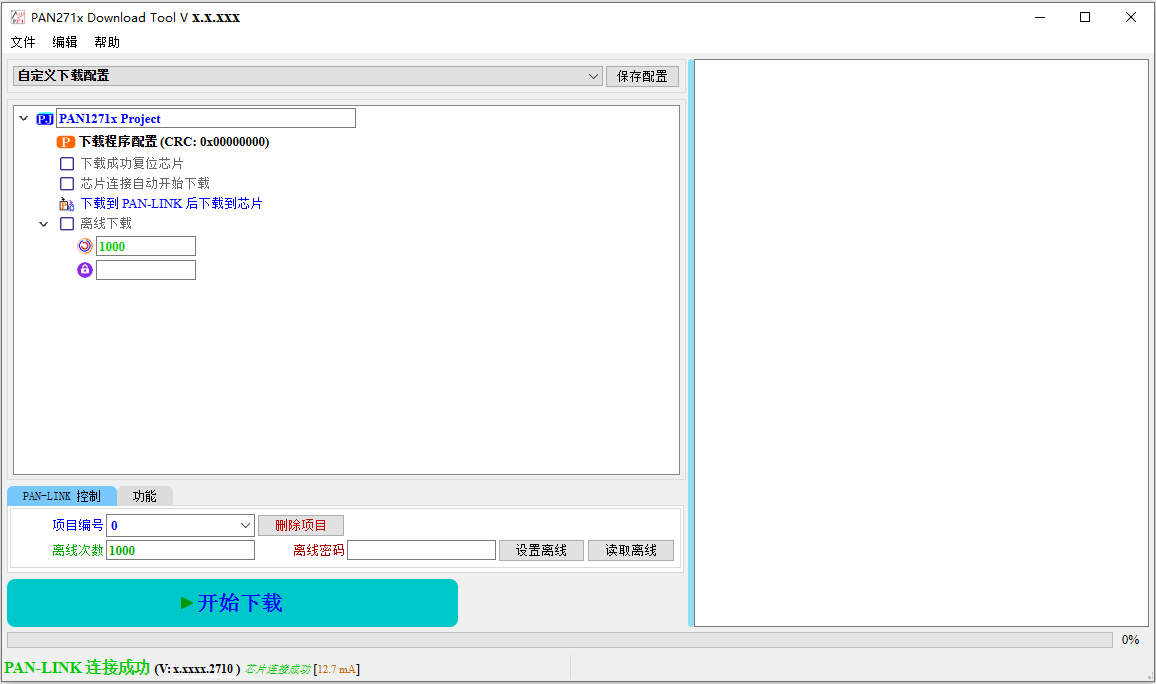

2 量产烧录工具¶

为配合 Panlink 2.0 烧录器进行量产烧录,我们提供了对应的 PC 上位机工具。

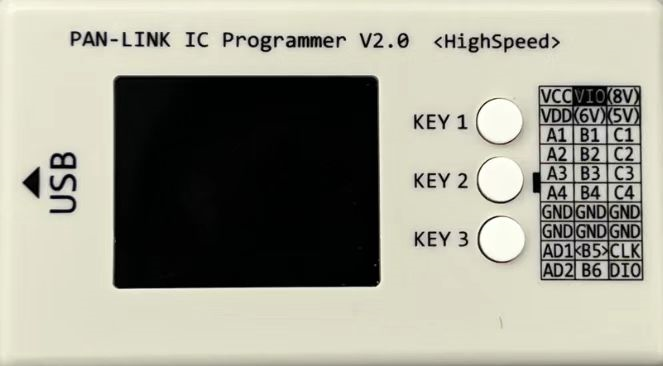

2.1 硬件准备¶

预先将 Panlink 2.0 通过 MiniUSB 线连接到 PC 电脑。

图2-1 Panlink 2.0 烧录器¶

图2-2 MiniUSB 连接线¶

如果 Panlink 2.0 固件程序不支持 PAN271芯片烧录,则需要根据提示自动更新升级。

或按照帮助文档方法更新 Panlink 2.0 固件程序。

PAN-LINK2.0 硬件需要特殊处理才能够烧录 PAN271x,否则无法连接。

PAN-LINK2.0 特殊处理:如果已经做了特殊处理则无需再做特殊处理。

图 2-3 Panlink 2.0 烧录器硬件需要特殊处理区域红色标注¶

PAN-LINK2.0 硬件 |

处理说明 |

|---|---|

R71 电阻 |

需要将原先的 220Ω 电阻更换为 1KΩ 电阻 |

R69 电阻 |

需要将原先的 10KΩ 电阻更换为 100 KΩ 以上阻值电阻 |

2.1.1 PAN271x 芯片烧录接线¶

Panlink 2.0 |

连接 |

PAN271x SoC |

|---|---|---|

VDD |

<—> |

VBAT |

(6V) |

<—> |

P22 |

GND |

<—> |

GND |

A3 |

<—> |

P01 |

A4 |

<—> |

P00 |

注:(6V) PAN-LINK 的 6.5V 高压输出,提供烧录 PAN271x 芯片 OTP 用。默认不输出,只有在执行烧录时才会自动控制输出。