PAN271x 硬件参考设计¶

1 原理图设计¶

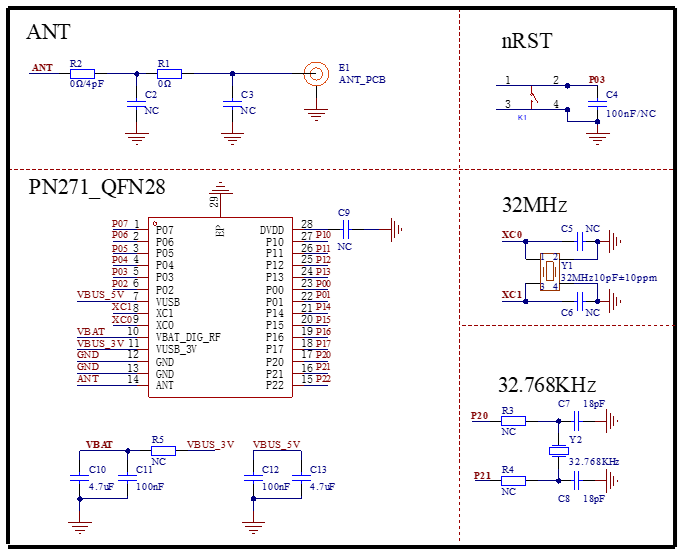

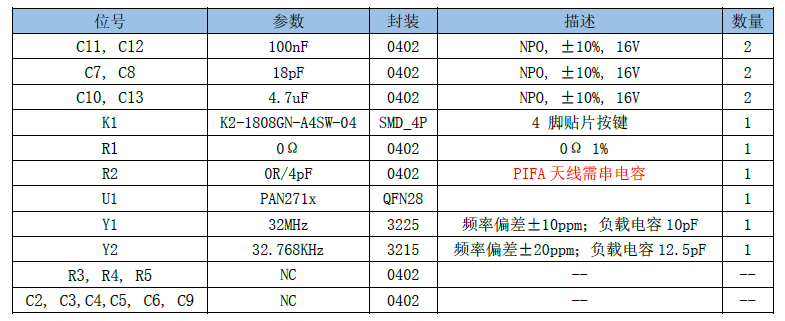

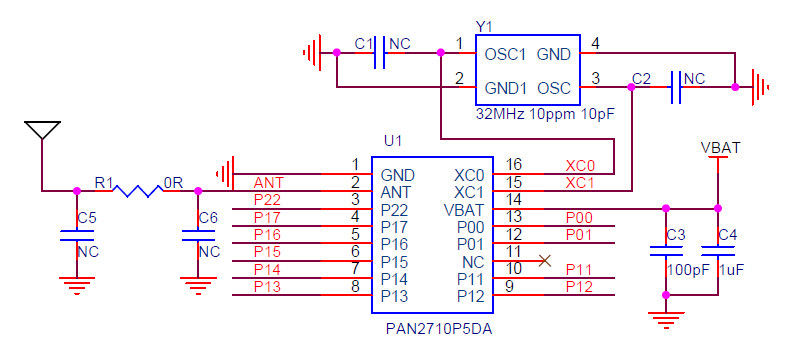

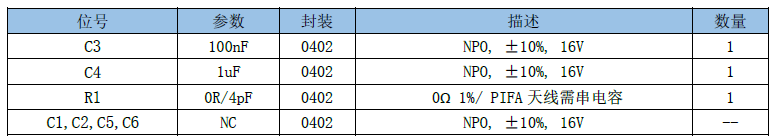

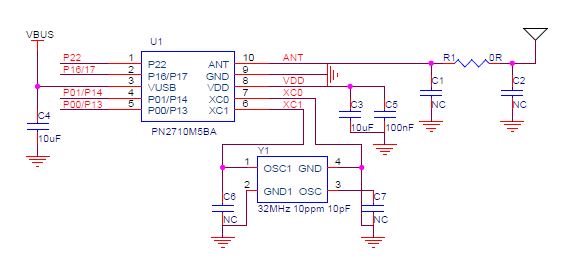

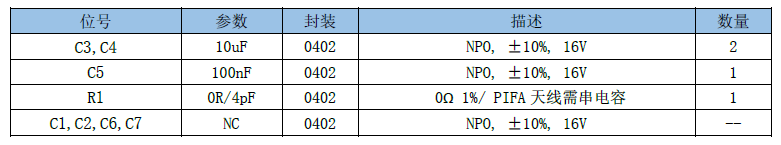

1.1 参考原理图¶

1.2 电源电路¶

电源设计的完整性影响芯片性能,好的电源设计更容易发挥无线模块的性能。电压范围 1.8-3.6V,纹波小于 ±100mV,频率小于 1MHz。电源设计需要留有裕量,一般来说,在条件允许的情况下,输出电流能力需要大于峰值电流的 2 倍。如果电流裕量有限,至少也需要 1.5 倍峰值电流以上。在 3.3V 供电系统中,过大的纹波可能通过导线或者地平面耦合到系统容易受到干扰的线路上,例如天线、馈线、时钟线等敏感信号线上,导致模块的射频性能变差。

电源供电有两种方式:

VBUS_5V 供电 5V,R5 焊接 0Ω(使 VBUS_3V 和 VBAT 短接)。 芯片内部有 LDO,会将 5V 转成 3.3V,从 VBUS_3V 输出,参考 QFN28 原理图。SOP16 没有 VBUS 管脚。

VBAT 供电 3.3V,R5 不焊接, 参考 QFN28 原理图。MSOP10 封装 VBUS 供电 5V,内部 3.3V 会接到 VDD 管脚,或单独在 VDD 供电 3.3V。

1.3 晶体电路¶

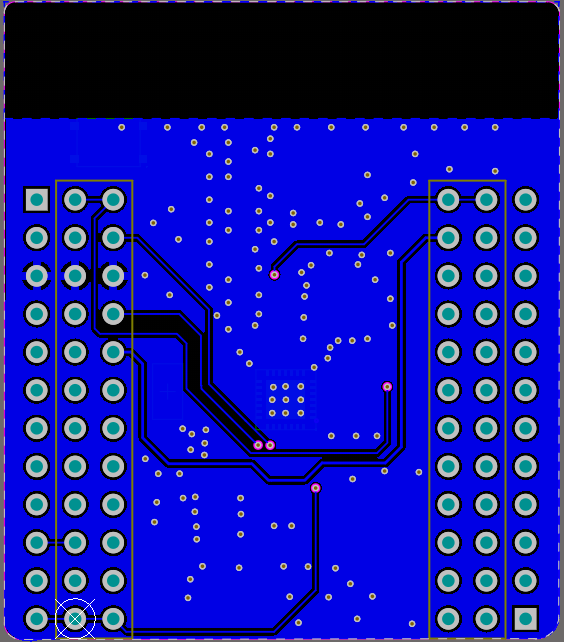

1.3.1 XTH 晶体推荐参数¶

晶体频率:32MHz或16MHz

ESR:小于80欧姆

晶体负载电容:10pF

频率偏差:±20ppm以内

1.3.2 XTL 晶体推荐参数¶

晶体频率:32.768KHz

ESR:小于40KΩ

晶体负载电容:12pF

频率偏差:±20ppm以内

1.4 天线匹配电路¶

天线匹配根据是否需要过 FCC/CE 认证来确定元器件参数。没有安规要求,建议匹配结构也预留(防止模组功率偏低需匹配优化),用 0 欧姆电阻串联到天线,PIFA 天线需串联 4pF 左右隔直电容到天线。

2 PCB 设计¶

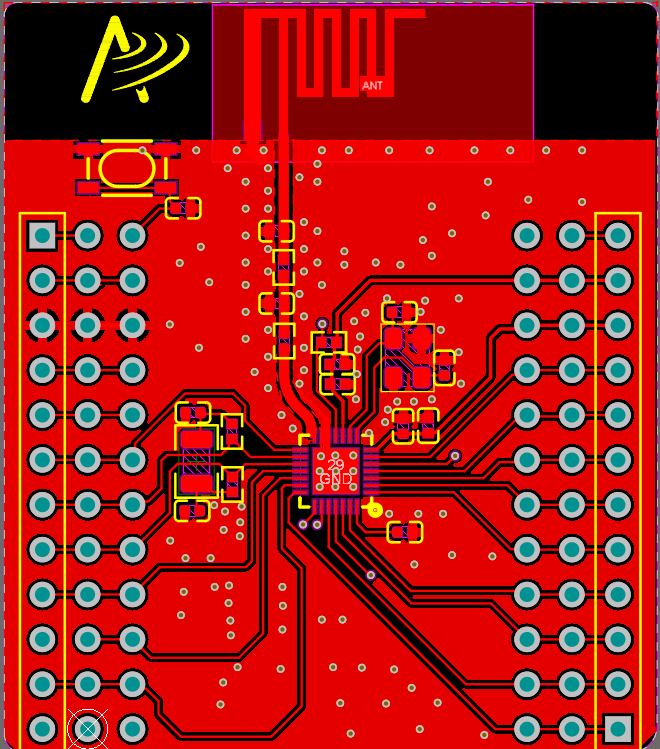

2.1 PCB 板材和叠层设计¶

板材建议优先选择双面FR4板材结构,最终叠层结构根据实际产品来确定。

2.2 电源和地线 Layout¶

电源线宽度尽量粗,尽量 20mil 以上。电源线必须先经过电容再到芯片电源输入管脚,在靠近芯片电源引脚放两个并联电容对电源低通滤波,其中小容值电容摆放在更靠近芯片引脚的位置,以便较好地滤除高频噪声。滤波电容接地保证较好的回流路径,双面板可以在地 PAD 就近打 VIA 减小回流路径。

建议电源线和地线采用放射状的连接方式,单点接电源/地并且单独走线,RF 芯片的电源/地线走线与其它芯片或器件分开,从总参考电源/地线单独引线,防止受到干扰,铺地推荐使用实心地。

铺地的地线建议与噪声较少的地线或者总参考地线连接,不与强信号或者强干扰器件地线相连,可以有效地减少整个印制板的工作噪声。

2.3 晶体电路 Layout¶

晶体至芯片管脚的走线尽量加粗,尽量短,不能走过孔

直插晶体的焊盘需要保证外径与内径差值有 0.2mm 以上

印制板上在晶体焊盘和走线的两边有完整地平面,最好不要有任何走线和元器件

为了避免干扰射频信号,晶体尽量远离射频走线

为避免大功率发射时,晶体受到辐射功率干扰,导致 RF 工作异常,晶振电路包括负载电容部分远离天线电路。PCB 天线部分与晶体电路之间尽量有地作为隔离带。

晶体布局示意图¶

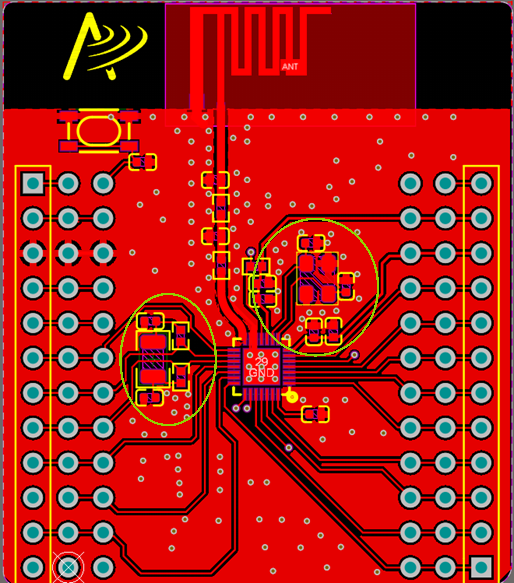

2.4 射频匹配电路 Layout¶

射频匹配电路对射频性能影响很大,因此需要特别注意。匹配元器件推荐用 0402 封装,匹配结构按参考原理图设计。射频匹配 layout 原则:

防止射频前端能量损耗,从 ANT 管脚到天线匹配电路的走线小于 2mm。天线 PI 型匹配电路要走顺,并联元件焊盘和走线重合为好,射频走线禁止打过孔换层。

射频走线宽度根据匹配器件是 0402/0603 封装适当调整。线宽控制在 0.5~1mm 之间。避免走线宽度和器件 pad 大小不一致,影响阻抗连续性。

射频走线两边需要良好铺地(多层板多打过孔)。铺地与射频走线间距,根据制板工艺,控制在 0.2~0.4mm 之间,同时满足 50 欧阻抗匹配。射频匹配部分对应背面,需要有完整的参考地平面,避免放置元器件和走线。

芯片有 EPAD,RF 参考地和 EPAD 需要良好连接,多层板需要在 EPAD 上打 4 个以上过孔与底层地连接

为了方便调试天线,ANT Pin 和 PI 型匹配之间可以串联 0R 电阻,电阻旁可以露一块 GND 属性铜皮。

2.5 天线 Layout¶

天线设计请参考 “2.4G PCB 天线设计指南”,文档请找技术支持获取。

PIFA 天线不能与地线铺铜靠很近,至少留空 1mm。天线部分对应的底层 PCB 严禁铺地。天线与参考地线铺铜间距要大于 1mm。天线周边最好不要有金属结构或元器件及走线,保证在 PCB 上间隔至少 3cm 范围内不摆放较大的带金属材质元器件。导线天线的馈点周围需要净空,净空区域要求 2mm 以上。

2.6 ESD 防护¶

敏感信号线需添加 ESD 保护管(常见 TVS)。TVS 摆放位置应尽可能靠近 ESD 源头(接头等处),与被保护 IC 的距离要远于 ESD 源。布线时需将 ESD 源直接接到 TVS,减少 TVS 管和回流地之间的寄生电感。

布线时,让敏感信号线远离 PCB 板边。为避免走线与天线间的串扰,走线需远离天线。

删除孤岛铜皮,用地将敏感信号包裹起来,降低干扰信号的辐射影响。

尽量增大过孔的钻孔直径和焊盘直径,减少过孔的寄生电感。

尽量缩短线长以减少寄生电感。因直角走线会产生更大的电磁辐射,避免直角走线连接到器件或走线上。