timer0_counter_mode例程¶

1 功能概述¶

本代码示例主要演示timer0(P1.5)的计数器功能。

2 环境要求¶

Board: PAN221x_EVB

逻辑分析仪

PANCHIP RISC IDE

3 编译和烧录¶

例程位置:PAN221x_DK_Public\01_SDK\basic_demo\timer\timer0_counter_mode

打开timer目录下timer0_counter_mode.sproj工程,编译整个代码工程。

4 测试方法¶

1、设置系统时钟源为dpll,并配置系统时钟为8Mhz;

2、设置P1.2和P1.3为输出模式,用于调试;

3、设置P1.5为输入模式;

4、将P1.2和P1.5用杜邦线连接,P1.2周期性的输出高低电平

5、设置timer0工作于计数器模式,待到达设定的计数次数,在中断中,翻转下P1.3;

6、通过杜邦线连接P1.2、P1.3到逻辑分析仪;

7、分析P1.3翻转的次数与设置的计数次数是否一致。

备注:timer0计数器计算方法如下:

定时器0计数次数 =(T0OVR[7:0] - T0C + 1);

5 测试现象¶

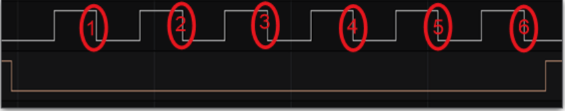

1、设置系统时钟为8Mhz,计数器的有效沿为下降沿,T0OVR = 0x5,T0C = 0x00,总的计数次数为:6次,检测到6次下降沿后,会触发中断,在中断中翻转一下P1.3,测试结果如下图所示:

计数器下降沿¶

上图的局部放大部分¶

2、设置系统时钟为8Mhz,计数器的有效沿为上升沿,T0OVR = 0x5,T0C = 0x00,总的计数次数为:6次,检测到6次下降沿后,会触发中断,在中断中翻转一下P1.3,测试结果如下图所示:

计数器上升沿¶

上图的局部放大部分¶

备注:如何配置计数器的有效沿: 上升沿:bset B_T0EDGE 下降沿:bclr B_T0EDGE

6 Rom/Ram资源使用情况¶

rom 86 bytes, ram 0 bytes