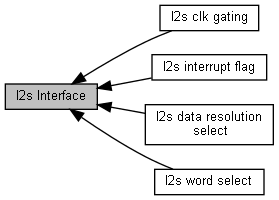

I2s Interface. More...

Modules | |

| I2s word select | |

| I2s word select cycles in the left or right sample mode. | |

| I2s clk gating | |

| I2s clk gating definition. | |

| I2s data resolution select | |

| I2s data resolution select definition. | |

| I2s interrupt flag | |

| I2s interrupt flag definition. | |

Macros | |

| #define | I2S_ENABLE_COMMON_BIT0 (1) |

| #define | I2S_SCLK_GATING_Pos (0) |

| #define | I2S_SCLK_GATING_Msk (0x7ul << I2S_SCLK_GATING_Pos) |

| #define | I2S_WORD_SELECT_LEN_Pos (3) |

| #define | I2S_WORD_SELECT_LEN_Msk (0x3ul << I2S_WORD_SELECT_LEN_Pos) |

| #define | I2S_WORD_LENGTH_SET_Pos (0) |

| #define | I2S_WORD_LENGTH_SET_Msk (0x7ul << I2S_WORD_LENGTH_SET_Pos) |

| #define | I2S_SINGLE_STEREO_BUFSEL_L (0) |

| #define | I2S_SINGLE_STEREO_BUFSEL_R (1) |

| #define | I2S_SINGLE_STEREO_TX (1<<16) |

| #define | I2S_SINGLE_TX_BUFSEL_Pos (17) |

| #define | I2S_SINGLE_TX_BUFSEL_Msk (1<<I2S_SINGLE_TX_BUFSEL_Pos) |

| #define | I2S_SINGLE_STEREO_RX (1<<18) |

| #define | I2S_SINGLE_RX_BUFSEL_Pos (19) |

| #define | I2S_SINGLE_RX_BUFSEL_Msk (1<<I2S_SINGLE_RX_BUFSEL_Pos) |

Functions | |

| __STATIC_INLINE void | I2S_EnableI2s (I2S_T *I2Sx) |

| Set I2s module enable. More... | |

| __STATIC_INLINE void | I2S_DisableI2s (I2S_T *I2Sx) |

| Set I2s module disable. More... | |

| __STATIC_INLINE void | I2S_EnableRecBlock (I2S_T *I2Sx) |

| Set I2s received block enable. More... | |

| __STATIC_INLINE void | I2S_DisableRecBlock (I2S_T *I2Sx) |

| Set I2s received block disable. More... | |

| __STATIC_INLINE void | I2S_EnableTransmitBlock (I2S_T *I2Sx) |

| Set I2s transmitter block enable. More... | |

| __STATIC_INLINE void | I2S_DisableTransmitBlock (I2S_T *I2Sx) |

| Set I2s transmitter block disable. More... | |

| __STATIC_INLINE void | I2S_EnableClk (I2S_T *I2Sx) |

| Set I2s CLK generation enable. More... | |

| __STATIC_INLINE void | I2S_DisableClk (I2S_T *I2Sx) |

| Set I2s CLK generation disable. More... | |

| __STATIC_INLINE void | I2S_SetRecFifoRst (I2S_T *I2Sx) |

| Set I2s receive fifo reset. More... | |

| __STATIC_INLINE void | I2S_SetTransmitFifoRst (I2S_T *I2Sx) |

| Set I2s transmitter fifo reset. More... | |

| __STATIC_INLINE void | I2S_EnRecChannel (I2S_T *I2Sx, uint8_t Ch) |

| Set I2s receive channel enable. More... | |

| __STATIC_INLINE void | I2S_DisableRecChannel (I2S_T *I2Sx, uint8_t Ch) |

| Set I2s receive channel disable. More... | |

| __STATIC_INLINE void | I2S_EnableTransmitCh (I2S_T *I2Sx, uint8_t Ch) |

| Set I2s transmitter channel enable. More... | |

| __STATIC_INLINE void | I2S_DisableTransmitCh (I2S_T *I2Sx, uint8_t Ch) |

| Set I2s transmitter channel disable. More... | |

| __STATIC_INLINE void | I2S_SetIntMsk (I2S_T *I2Sx, uint8_t Ch, uint8_t Msk) |

| Set I2s interrupt mask. More... | |

| __STATIC_INLINE void | I2S_ClearIntMsk (I2S_T *I2Sx, uint8_t Ch, uint8_t Msk) |

| Clear I2s interrupt mask. More... | |

| __STATIC_INLINE bool | I2S_IsIntMsk (I2S_T *I2Sx, uint8_t Ch, uint8_t Msk) |

| Set I2s interrupt mask. More... | |

| __STATIC_INLINE void | I2S_SetRxTrigLevel (I2S_T *I2Sx, uint8_t Ch, uint8_t Level) |

| Set I2s rx trigger level. More... | |

| __STATIC_INLINE void | I2S_SetTxTrigLevel (I2S_T *I2Sx, uint8_t Ch, uint8_t Level) |

| Set I2s tx trigger level. More... | |

| __STATIC_INLINE void | I2S_SetRecChFifoRst (I2S_T *I2Sx, uint8_t Ch) |

| Set I2s receive channel fifo reset. More... | |

| __STATIC_INLINE void | I2S_SetTransmitChFifoRst (I2S_T *I2Sx, uint8_t Ch) |

| Set I2s transmitter channel fifo reset. More... | |

| __STATIC_INLINE void | I2S_WriteTxDmaDat (I2S_T *I2Sx, uint32_t Data) |

| Write I2s tx dma data. More... | |

| __STATIC_INLINE uint32_t | I2S_ReadRxDmaDat (I2S_T *I2Sx) |

| Read I2s rx dma data. More... | |

| __STATIC_INLINE uint8_t | I2S_GetIntStatus (I2S_T *I2Sx, uint8_t Ch) |

| Get I2s interrupt status. More... | |

| __STATIC_INLINE bool | I2S_IsIntOccured (I2S_T *I2Sx, uint8_t Ch, uint8_t Msk) |

| Adjust which i2s interrupt occured. More... | |

| __STATIC_INLINE void | I2S_WriteLeftTransmitData (I2S_T *I2Sx, uint8_t Ch, uint16_t Data) |

| Write I2s left transmitter data. More... | |

| __STATIC_INLINE uint16_t | I2S_ReadLeftRecData (I2S_T *I2Sx, uint8_t Ch) |

| Read I2s left receive data. More... | |

| __STATIC_INLINE void | I2S_WriteRightTransmitData (I2S_T *I2Sx, uint8_t Ch, uint16_t Data) |

| Write I2s right transmitter data. More... | |

| __STATIC_INLINE uint16_t | I2S_ReadRightRecData (I2S_T *I2Sx, uint8_t Ch) |

| Read I2s left receive data. More... | |

| __STATIC_INLINE void | I2S_TxSingleStereoEnable (I2S_T *I2Sx, bool enable) |

| Enable I2s single stereo TX function. More... | |

| __STATIC_INLINE void | I2S_TxSingleStereoBufSel (I2S_T *I2Sx, uint32_t bufSel) |

| buffer select in single stereo TX mode More... | |

| __STATIC_INLINE void | I2S_RxSingleStereoEnable (I2S_T *I2Sx, bool enable) |

| Enable I2s single stereo RX function. More... | |

| __STATIC_INLINE void | I2S_RxSingleStereoBufSel (I2S_T *I2Sx, uint32_t bufSel) |

| buffer select in single stereo TX mode More... | |

| void | I2S_SetWordSelectLen (I2S_T *i2s, uint8_t u8WordSel) |

| set I2s word select lenth,default 16 clk cycle More... | |

| void | I2S_SetSclkGate (I2S_T *i2s, uint8_t u8SclkSel) |

| set I2s clk gating cycle,default:no gating More... | |

| void | I2S_SetRecWordLen (I2S_T *i2s, uint8_t ch, uint8_t u8WordLen) |

| set I2s receive word length resolution,default:no word length More... | |

| void | I2S_SetTrmWordLen (I2S_T *i2s, uint8_t ch, uint8_t u8WordLen) |

| set I2s transmitter word length resolution,default:no word length More... | |

| uint32_t | I2S_ClearRxOverInt (I2S_T *i2s, uint8_t ch) |

| Clear rx fifo over interrupt status. More... | |

| uint32_t | I2S_ClearTxOverInt (I2S_T *i2s, uint8_t ch) |

| Clear tx fifo over interrupt status. More... | |

| void | I2S_Send (I2S_T *I2Sx, uint8_t Ch, uint32_t *LeftBuf, uint32_t *RightBuf, uint32_t Size) |

| I2S send data. More... | |

| void | I2S_Receive (I2S_T *I2Sx, uint8_t Ch, uint32_t *LeftBuf, uint32_t *RightBuf, uint32_t Size) |

| I2S send data. More... | |

Detailed Description

I2s Interface.

Macro Definition Documentation

◆ I2S_ENABLE_COMMON_BIT0

| #define I2S_ENABLE_COMMON_BIT0 (1) |

General common bit value

◆ I2S_SCLK_GATING_Msk

| #define I2S_SCLK_GATING_Msk (0x7ul << I2S_SCLK_GATING_Pos) |

I2s sclk gating control bit mask value

◆ I2S_SCLK_GATING_Pos

| #define I2S_SCLK_GATING_Pos (0) |

Position of I2s sclk gating control bit

◆ I2S_SINGLE_RX_BUFSEL_Msk

| #define I2S_SINGLE_RX_BUFSEL_Msk (1<<I2S_SINGLE_RX_BUFSEL_Pos) |

I2s singal stereo receive buffer select control bit mask value

◆ I2S_SINGLE_RX_BUFSEL_Pos

| #define I2S_SINGLE_RX_BUFSEL_Pos (19) |

Position of I2s singal stereo receive buffer select control bit

◆ I2S_SINGLE_STEREO_BUFSEL_L

| #define I2S_SINGLE_STEREO_BUFSEL_L (0) |

I2s left buffer selected

◆ I2S_SINGLE_STEREO_BUFSEL_R

| #define I2S_SINGLE_STEREO_BUFSEL_R (1) |

I2s right buffer selected

◆ I2S_SINGLE_STEREO_RX

| #define I2S_SINGLE_STEREO_RX (1<<18) |

I2s singal stereo receive enable bit

◆ I2S_SINGLE_STEREO_TX

| #define I2S_SINGLE_STEREO_TX (1<<16) |

I2s singal stereo transmit enable bit

◆ I2S_SINGLE_TX_BUFSEL_Msk

| #define I2S_SINGLE_TX_BUFSEL_Msk (1<<I2S_SINGLE_TX_BUFSEL_Pos) |

I2s singal stereo transmit buffer select control bit mask value

◆ I2S_SINGLE_TX_BUFSEL_Pos

| #define I2S_SINGLE_TX_BUFSEL_Pos (17) |

Position of I2s singal stereo transmit buffer select control bit

◆ I2S_WORD_LENGTH_SET_Msk

| #define I2S_WORD_LENGTH_SET_Msk (0x7ul << I2S_WORD_LENGTH_SET_Pos) |

I2s data resolution control bit mask value

◆ I2S_WORD_LENGTH_SET_Pos

| #define I2S_WORD_LENGTH_SET_Pos (0) |

Position of I2s data resolution control bit

◆ I2S_WORD_SELECT_LEN_Msk

| #define I2S_WORD_SELECT_LEN_Msk (0x3ul << I2S_WORD_SELECT_LEN_Pos) |

I2s word lenth select control bit mask value

◆ I2S_WORD_SELECT_LEN_Pos

| #define I2S_WORD_SELECT_LEN_Pos (3) |

Position of I2s word lenth select control bit

Function Documentation

◆ I2S_ClearIntMsk()

| __STATIC_INLINE void I2S_ClearIntMsk | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint8_t | Msk | ||

| ) |

Clear I2s interrupt mask.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select Msk interrupt status: I2S_INT_TX_OVER I2S_INT_TX_EMPTY I2S_INT_RX_OVER I2S_INT_RX_VALID

- Returns

- None

◆ I2S_ClearRxOverInt()

| uint32_t I2S_ClearRxOverInt | ( | I2S_T * | i2s, |

| uint8_t | ch | ||

| ) |

Clear rx fifo over interrupt status.

- Parameters

-

i2s The base address of i2s module ch i2s channel select

- Return values

-

NONE

◆ I2S_ClearTxOverInt()

| uint32_t I2S_ClearTxOverInt | ( | I2S_T * | i2s, |

| uint8_t | ch | ||

| ) |

Clear tx fifo over interrupt status.

- Parameters

-

i2s The base address of i2s module ch i2s channel select

- Return values

-

NONE

◆ I2S_DisableClk()

| __STATIC_INLINE void I2S_DisableClk | ( | I2S_T * | I2Sx | ) |

Set I2s CLK generation disable.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_DisableI2s()

| __STATIC_INLINE void I2S_DisableI2s | ( | I2S_T * | I2Sx | ) |

Set I2s module disable.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_DisableRecBlock()

| __STATIC_INLINE void I2S_DisableRecBlock | ( | I2S_T * | I2Sx | ) |

Set I2s received block disable.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_DisableRecChannel()

| __STATIC_INLINE void I2S_DisableRecChannel | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Set I2s receive channel disable.

- Parameters

-

I2Sx The base address of i2s module Ch I2s channel select

- Returns

- None

◆ I2S_DisableTransmitBlock()

| __STATIC_INLINE void I2S_DisableTransmitBlock | ( | I2S_T * | I2Sx | ) |

Set I2s transmitter block disable.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_DisableTransmitCh()

| __STATIC_INLINE void I2S_DisableTransmitCh | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Set I2s transmitter channel disable.

- Parameters

-

I2Sx The base address of i2s module Ch I2s channel select

- Returns

- None

◆ I2S_EnableClk()

| __STATIC_INLINE void I2S_EnableClk | ( | I2S_T * | I2Sx | ) |

Set I2s CLK generation enable.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_EnableI2s()

| __STATIC_INLINE void I2S_EnableI2s | ( | I2S_T * | I2Sx | ) |

Set I2s module enable.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_EnableRecBlock()

| __STATIC_INLINE void I2S_EnableRecBlock | ( | I2S_T * | I2Sx | ) |

Set I2s received block enable.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_EnableTransmitBlock()

| __STATIC_INLINE void I2S_EnableTransmitBlock | ( | I2S_T * | I2Sx | ) |

Set I2s transmitter block enable.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_EnableTransmitCh()

| __STATIC_INLINE void I2S_EnableTransmitCh | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Set I2s transmitter channel enable.

- Parameters

-

I2Sx The base address of i2s module Ch I2s channel number

- Returns

- None

◆ I2S_EnRecChannel()

| __STATIC_INLINE void I2S_EnRecChannel | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Set I2s receive channel enable.

- Parameters

-

I2Sx The base address of i2s module Ch I2s channel select

- Returns

- None

◆ I2S_GetIntStatus()

| __STATIC_INLINE uint8_t I2S_GetIntStatus | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Get I2s interrupt status.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select

- Returns

- Interrupt status

◆ I2S_IsIntMsk()

| __STATIC_INLINE bool I2S_IsIntMsk | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint8_t | Msk | ||

| ) |

Set I2s interrupt mask.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select Msk interrupt status: I2S_INT_TX_OVER I2S_INT_TX_EMPTY I2S_INT_RX_OVER I2S_INT_RX_VALID

- Returns

- true or false

◆ I2S_IsIntOccured()

| __STATIC_INLINE bool I2S_IsIntOccured | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint8_t | Msk | ||

| ) |

Adjust which i2s interrupt occured.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select Msk interrupt status: I2S_INT_TX_OVER I2S_INT_TX_EMPTY I2S_INT_RX_OVER I2S_INT_RX_VALID

- Returns

- None

◆ I2S_ReadLeftRecData()

| __STATIC_INLINE uint16_t I2S_ReadLeftRecData | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Read I2s left receive data.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select

- Returns

- Left receive data

◆ I2S_ReadRightRecData()

| __STATIC_INLINE uint16_t I2S_ReadRightRecData | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Read I2s left receive data.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select

- Returns

- Right receive data

◆ I2S_ReadRxDmaDat()

| __STATIC_INLINE uint32_t I2S_ReadRxDmaDat | ( | I2S_T * | I2Sx | ) |

Read I2s rx dma data.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_Receive()

| void I2S_Receive | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint32_t * | LeftBuf, | ||

| uint32_t * | RightBuf, | ||

| uint32_t | Size | ||

| ) |

I2S send data.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select LeftBuf left channel data buffer RightBuf right channel data buffer Size send data number

- Return values

-

NONE

◆ I2S_RxSingleStereoBufSel()

| __STATIC_INLINE void I2S_RxSingleStereoBufSel | ( | I2S_T * | I2Sx, |

| uint32_t | bufSel | ||

| ) |

buffer select in single stereo TX mode

- Parameters

-

i2s The base address of i2s module bufSel left or right stereo select

- Return values

-

none

◆ I2S_RxSingleStereoEnable()

| __STATIC_INLINE void I2S_RxSingleStereoEnable | ( | I2S_T * | I2Sx, |

| bool | enable | ||

| ) |

Enable I2s single stereo RX function.

- Parameters

-

i2s The base address of i2s module enable RX single stereo enable or not

- Return values

-

none

◆ I2S_Send()

| void I2S_Send | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint32_t * | LeftBuf, | ||

| uint32_t * | RightBuf, | ||

| uint32_t | Size | ||

| ) |

I2S send data.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select LeftBuf left channel data buffer RightBuf right channel data buffer Size send data number

- Return values

-

NONE

◆ I2S_SetIntMsk()

| __STATIC_INLINE void I2S_SetIntMsk | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint8_t | Msk | ||

| ) |

Set I2s interrupt mask.

- Parameters

-

I2Sx The base address of i2s module Ch I2s channel select Msk interrupt status: I2S_INT_TX_OVER I2S_INT_TX_EMPTY I2S_INT_RX_OVER I2S_INT_RX_VALID

- Returns

- None

◆ I2S_SetRecChFifoRst()

| __STATIC_INLINE void I2S_SetRecChFifoRst | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Set I2s receive channel fifo reset.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select

- Returns

- None

◆ I2S_SetRecFifoRst()

| __STATIC_INLINE void I2S_SetRecFifoRst | ( | I2S_T * | I2Sx | ) |

Set I2s receive fifo reset.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_SetRecWordLen()

| void I2S_SetRecWordLen | ( | I2S_T * | i2s, |

| uint8_t | ch, | ||

| uint8_t | u8WordLen | ||

| ) |

set I2s receive word length resolution,default:no word length

- Parameters

-

i2s The base address of i2s module ch i2s channel select u8WordLen word length resolution select: I2S_WORD_LEN_IGNORE I2S_WORD_LEN_12_BIT_RESOLUTION I2S_WORD_LEN_16_BIT_RESOLUTION I2S_WORD_LEN_20_BIT_RESOLUTION I2S_WORD_LEN_24_BIT_RESOLUTION I2S_WORD_LEN_32_BIT_RESOLUTION

- Returns

- None

◆ I2S_SetRxTrigLevel()

| __STATIC_INLINE void I2S_SetRxTrigLevel | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint8_t | Level | ||

| ) |

Set I2s rx trigger level.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select Level trigger level

- Returns

- none

◆ I2S_SetSclkGate()

| void I2S_SetSclkGate | ( | I2S_T * | i2s, |

| uint8_t | u8SclkSel | ||

| ) |

set I2s clk gating cycle,default:no gating

- Parameters

-

i2s The base address of i2s module u8SclkSel gating select: I2S_CLK_GATING_SEL_0_CYCLE I2S_CLK_GATING_SEL_12_CYCLE I2S_CLK_GATING_SEL_16_CYCLE I2S_CLK_GATING_SEL_24_CYCLE I2S_CLK_GATING_SEL_32_CYCLE

- Returns

- None

◆ I2S_SetTransmitChFifoRst()

| __STATIC_INLINE void I2S_SetTransmitChFifoRst | ( | I2S_T * | I2Sx, |

| uint8_t | Ch | ||

| ) |

Set I2s transmitter channel fifo reset.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select

- Returns

- None

◆ I2S_SetTransmitFifoRst()

| __STATIC_INLINE void I2S_SetTransmitFifoRst | ( | I2S_T * | I2Sx | ) |

Set I2s transmitter fifo reset.

- Parameters

-

I2Sx The base address of i2s module

- Returns

- None

◆ I2S_SetTrmWordLen()

| void I2S_SetTrmWordLen | ( | I2S_T * | i2s, |

| uint8_t | ch, | ||

| uint8_t | u8WordLen | ||

| ) |

set I2s transmitter word length resolution,default:no word length

- Parameters

-

i2s The base address of i2s module ch i2s channel select u8WordLen word length resolution select: I2S_WORD_LEN_IGNORE I2S_WORD_LEN_12_BIT_RESOLUTION I2S_WORD_LEN_16_BIT_RESOLUTION I2S_WORD_LEN_20_BIT_RESOLUTION I2S_WORD_LEN_24_BIT_RESOLUTION I2S_WORD_LEN_32_BIT_RESOLUTION

- Return values

-

None

◆ I2S_SetTxTrigLevel()

| __STATIC_INLINE void I2S_SetTxTrigLevel | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint8_t | Level | ||

| ) |

Set I2s tx trigger level.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select Level trigger level

- Returns

- None

◆ I2S_SetWordSelectLen()

| void I2S_SetWordSelectLen | ( | I2S_T * | i2s, |

| uint8_t | u8WordSel | ||

| ) |

set I2s word select lenth,default 16 clk cycle

- Parameters

-

i2s The base address of i2s module u8WordSel sclk cycle select I2S_WORD_SEL_16_CYCLE I2S_WORD_SEL_24_CYCLE I2S_WORD_SEL_32_CYCLE

- Returns

- None

◆ I2S_TxSingleStereoBufSel()

| __STATIC_INLINE void I2S_TxSingleStereoBufSel | ( | I2S_T * | I2Sx, |

| uint32_t | bufSel | ||

| ) |

buffer select in single stereo TX mode

- Parameters

-

i2s The base address of i2s module bufSel left or right stereo select

- Return values

-

none

◆ I2S_TxSingleStereoEnable()

| __STATIC_INLINE void I2S_TxSingleStereoEnable | ( | I2S_T * | I2Sx, |

| bool | enable | ||

| ) |

Enable I2s single stereo TX function.

- Parameters

-

i2s The base address of i2s module enable TX single stereo enable or not

- Return values

-

none

◆ I2S_WriteLeftTransmitData()

| __STATIC_INLINE void I2S_WriteLeftTransmitData | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint16_t | Data | ||

| ) |

Write I2s left transmitter data.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select Data write data,16bit data aligned

- Returns

- None

◆ I2S_WriteRightTransmitData()

| __STATIC_INLINE void I2S_WriteRightTransmitData | ( | I2S_T * | I2Sx, |

| uint8_t | Ch, | ||

| uint16_t | Data | ||

| ) |

Write I2s right transmitter data.

- Parameters

-

I2Sx The base address of i2s module Ch i2s channel select Data write data,16bit data aligned

- Returns

- None

◆ I2S_WriteTxDmaDat()

| __STATIC_INLINE void I2S_WriteTxDmaDat | ( | I2S_T * | I2Sx, |

| uint32_t | Data | ||

| ) |

Write I2s tx dma data.

- Parameters

-

I2Sx The base address of i2s module Data write data

- Returns

- None