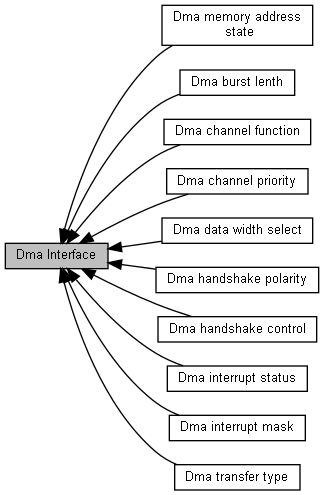

Dma Interface. More...

Modules | |

| Dma transfer type | |

| Dma transfer type definition. | |

| Dma burst lenth | |

| Dma burst lenth definition. | |

| Dma memory address state | |

| Dma memory address state definition. | |

| Dma data width select | |

| Dma data width select definition. | |

| Dma channel function | |

| Dma channel function definition. | |

| Dma handshake polarity | |

| Dma handshake polarity definition. | |

| Dma handshake control | |

| Dma handshake control definition. | |

| Dma channel priority | |

| Dma channel priority definition. | |

| Dma interrupt status | |

| Dma interrupt status definition. | |

| Dma interrupt mask | |

| Dma interrupt mask definition. | |

Data Structures | |

| struct | __DMAC_ChannelConfigTypeDef |

| Structure with dma channel config feature. More... | |

| struct | DMAC_ChannelConfigTypeDef |

| Structure with dma channel detail config. More... | |

Macros | |

| #define | DMAC_CHANNEL_NUMBER (3) |

| #define | DMA_INVLID_CHANNEL (~0ul) |

| #define | DMAC_FlowControl_DMA (0) |

| #define | DMAC_FlowControl_Peripheral (1) |

| #define | DMAC_LockLevel_Tfr_Complete (0) |

| #define | DMAC_LockLevel_Block_Complete (1) |

| #define | DMAC_LockLevel_Transaction_Complete (2) |

| #define | DMAC_CHANNELALL_MASK (~((~0ul)<<DMAC_CHANNEL_NUMBER)) |

| #define | DMAC_ChannelMask(idx) (1ul<<(idx)) |

| :Set interrupt mask of one dma channel More... | |

Typedefs | |

| typedef struct __DMAC_ChannelConfigTypeDef | __DMAC_ChannelConfigTypeDef |

| Structure with dma channel config feature. More... | |

| typedef struct DMAC_ChannelConfigTypeDef | DMAC_ChannelConfigTypeDef |

| Structure with dma channel detail config. More... | |

Functions | |

| __STATIC_INLINE uint32_t | DMAC_IsChannelValid (DMA_T *dma, uint32_t ChIdx) |

| Adjust dma channel is busy or not. More... | |

| __STATIC_INLINE uint32_t | DMAC_CombinedIntStatus (DMA_T *dma, uint32_t FlgMsk) |

| Adjust interrupt occured or not. More... | |

| __STATIC_INLINE uint32_t | DMAC_StatusFlag (DMA_T *dma, uint32_t ChIdx, uint32_t FlgIdx) |

| Adjust interrupt raw flag set or not. More... | |

| __STATIC_INLINE uint32_t | DMAC_IntFlag (DMA_T *dma, uint32_t ChIdx, uint32_t FlgIdx) |

| Adjust interrupt event occured or not after masking. More... | |

| __STATIC_INLINE uint32_t | DMAC_IntFlagMsk (DMA_T *dma, uint32_t ChIdx, uint32_t FlgIdx) |

| Adjust interrupt mask set or not. More... | |

| __STATIC_INLINE void | DMAC_ClrIntFlag (DMA_T *dma, uint32_t ChIdx, uint32_t FlgIdx) |

| Adjust interrupt mask cleared or not. More... | |

| void | DMAC_Init (DMA_T *dma) |

| Enable dma. More... | |

| void | DMAC_DeInit (DMA_T *dma) |

| Disable dma & mask all dma interrupt. More... | |

| void | DMAC_ClrIntFlagMsk (DMA_T *dma, uint32_t ChIdx, uint32_t FlgIdx) |

| Clear interrupt mask to make sure intterupt enable. More... | |

| void | DMAC_SetIntFlagMsk (DMA_T *dma, uint32_t ChIdx, uint32_t FlgIdx) |

| Mask interrupt,interrupt is useless. More... | |

| void | DMAC_SetChannelConfig (DMA_T *dma, uint32_t ChIdx, DMAC_ChannelConfigTypeDef *Config) |

| Set dma channel config,include control register and config register. More... | |

| void | DMAC_GetChannelConfig (DMA_T *dma, uint32_t ChIdx, DMAC_ChannelConfigTypeDef *Config) |

| Get dma channel config,include control register and config register. More... | |

| void | DMAC_StartChannel (DMA_T *dma, uint32_t ChIdx, void *Src, void *Dst, uint32_t Len) |

| Start dma channel to transmit. More... | |

| void | DMAC_StopChannel (DMA_T *dma, uint32_t ChIdx) |

| Stop dma channel. More... | |

| uint32_t | DMAC_AcquireChannel (DMA_T *dma) |

| Acquire dma free channel. More... | |

| void | DMAC_ReleaseChannel (DMA_T *dma, uint32_t ChIdx) |

| Release dma channel. More... | |

Detailed Description

Dma Interface.

Macro Definition Documentation

◆ DMA_INVLID_CHANNEL

| #define DMA_INVLID_CHANNEL (~0ul) |

return value after acquire no dma channel

◆ DMAC_CHANNEL_NUMBER

| #define DMAC_CHANNEL_NUMBER (3) |

Number of available dma channels

◆ DMAC_CHANNELALL_MASK

| #define DMAC_CHANNELALL_MASK (~((~0ul)<<DMAC_CHANNEL_NUMBER)) |

Set interrupt mask of all dma channel

◆ DMAC_ChannelMask

| #define DMAC_ChannelMask | ( | idx | ) | (1ul<<(idx)) |

:Set interrupt mask of one dma channel

- Parameters

-

:Where idx is the dma channel number.It could be 0,1,2

- Returns

- :None

◆ DMAC_FlowControl_DMA

| #define DMAC_FlowControl_DMA (0) |

Flow controlled by dma

◆ DMAC_FlowControl_Peripheral

| #define DMAC_FlowControl_Peripheral (1) |

Flow controlled by peripheral

◆ DMAC_LockLevel_Block_Complete

| #define DMAC_LockLevel_Block_Complete (1) |

Over complete DMA block transfer

◆ DMAC_LockLevel_Tfr_Complete

| #define DMAC_LockLevel_Tfr_Complete (0) |

Over complete DMA transfer

◆ DMAC_LockLevel_Transaction_Complete

| #define DMAC_LockLevel_Transaction_Complete (2) |

Over complete DMA transaction

Typedef Documentation

◆ __DMAC_ChannelConfigTypeDef

| typedef struct __DMAC_ChannelConfigTypeDef __DMAC_ChannelConfigTypeDef |

Structure with dma channel config feature.

- Parameters

-

CTL_L Low 32 bit of dma channel control register. CTL_H High 32 bit of dma channel control register. CFG_L Low 32 bit of dma channel config register. CFG_H High 32 bit of dma channel config register.

◆ DMAC_ChannelConfigTypeDef

| typedef struct DMAC_ChannelConfigTypeDef DMAC_ChannelConfigTypeDef |

Structure with dma channel detail config.

- Parameters

-

IntEnable Interrupt enable bit. DataWidthDst Destination data width. Dma data width select DataWidthSrc Source data width. Dma data width select AddrChangeDst Destination address change. Dma memory address state AddrChangeSrc Source address change. Dma memory address state BurstLenDst Destination burst transaction length. Dma burst lenth BurstLenSrc Source burst transaction length. Dma burst lenth GatherEnSrc Source gather enable bit. ScatterEnDst Destination scatter enable bit. __Rev0 reversed bit. TransferType Transfer Type. Dma transfer type FlowControl Flow Control DMAC_FlowControl_Peripheral, DMAC_FlowControl_DMA __Rev1 reversed bit. BlockSize Block size number ,block_size = data_len / DataWidth. Done Done flag. __Rev2 reversed bit. __Rev3 reversed bit. ChannelPriority Channel priority,it can be 0~7,the priority 7 is the highest. ChannelSuspend Channel Suspend,transfer is not complete ,set this bit can stop transmit. FifoEmpty Indicates if there is data left in the channel FIFO HandshakeDst Destination Handshake select:software or hardware HandshakeSrc Source Handshake select:software or hardware LockBus When active, the AHB bus master signal hlock is asserted for the duration specified in CFGx.LOCK_B_L. LockChannel When the channel is granted control of the master bus interface and if the CFGx.LOCK_CH bit is asserted,then no other channels are granted control of the master bus interface for the duration specified in CFGx.LOCK_CH_L LockBusLevel Indicates the duration over which CFGx.LOCK_B bit applies. LockChannelLevel Indicates the duration over which CFGx.LOCK_CH bit applies. HandshakePolarityDst Destination Handshaking Interface Polarity:0-high, 1-low. HandshakePolaritySrc Source Handshaking Interface Polarity:0-high, 1-low. __Rev4 reversed bit. AutoReloadSrc Automatic Source Reload. AutoReloadDst Automatic Destination Reload. FlowControlMode Determines when source transaction requests are serviced when the Destination Peripheral is the flow controller. FifoMode Determines how much space or data needs to be available in the FIFO. ProtectControl Used to drive the AHB HPROT[3:1] bus. __Rev5 reversed bit. PeripheralSrc Assigns a hardware handshaking interface to the source of channel x if the CFGx.HS_SEL_SRC field is 0 PeripheralDst Assigns a hardware handshaking interface to the destination of channel x if the CFGx.HS_SEL_DST field is 0 __Rev6 reversed bit.

Function Documentation

◆ DMAC_AcquireChannel()

| uint32_t DMAC_AcquireChannel | ( | DMA_T * | dma | ) |

Acquire dma free channel.

- Parameters

-

dma Where dma is the base address of dma peripheral

- Returns

- None

◆ DMAC_ClrIntFlag()

| __STATIC_INLINE void DMAC_ClrIntFlag | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| uint32_t | FlgIdx | ||

| ) |

Adjust interrupt mask cleared or not.

- Parameters

-

dma where dma is the base address of dma peripheral ChIdx where ChIdx is the dma channel number.It could be 0,1,2 FlgIdx where FlgIdx is interrupt type,It could be:Dma interrupt status

- Returns

- None

◆ DMAC_ClrIntFlagMsk()

| void DMAC_ClrIntFlagMsk | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| uint32_t | FlgIdx | ||

| ) |

Clear interrupt mask to make sure intterupt enable.

- Parameters

-

dma Where dma is the base address of dma peripheral ChIdx Where ChIdx is the dma channel number.It could be 0,1,2 FlgIdx Where FlgIdx is interrupt type,It could be: DMAC_FLAG_INDEX_TFR

DMAC_FLAG_INDEX_BLK

DMAC_FLAG_INDEX_SRCTFR DMAC_FLAG_INDEX_DSTTFR DMAC_FLAG_INDEX_ERR

- Returns

- None

◆ DMAC_CombinedIntStatus()

| __STATIC_INLINE uint32_t DMAC_CombinedIntStatus | ( | DMA_T * | dma, |

| uint32_t | FlgMsk | ||

| ) |

Adjust interrupt occured or not.

- Parameters

-

dma Where dma is the base address of dma peripheral FlgMsk Where flgMsk is combined interrupt status ,it could be: DMAC_FLAG_MASK_TFR

DMAC_FLAG_MASK_BLK

DMAC_FLAG_MASK_SRCTFR DMAC_FLAG_MASK_DSTTFR DMAC_FLAG_MASK_ERR

DMAC_FLAG_MASK_ALL

- Return values

-

0 dma interrupt did not occurred 1 dma interrupt occurred

◆ DMAC_DeInit()

| void DMAC_DeInit | ( | DMA_T * | dma | ) |

Disable dma & mask all dma interrupt.

- Parameters

-

dma Where dma is the base address of dma peripheral

- Returns

- None

◆ DMAC_GetChannelConfig()

| void DMAC_GetChannelConfig | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| DMAC_ChannelConfigTypeDef * | Config | ||

| ) |

Get dma channel config,include control register and config register.

- Parameters

-

dma Where dma is the base address of dma peripheral ChIdx Where ChIdx is the dma channel number.It could be 0,1,2 Config Where Config is the config of dma channel. DMAC_ChannelConfigTypeDef

- Returns

- None

◆ DMAC_Init()

| void DMAC_Init | ( | DMA_T * | dma | ) |

Enable dma.

- Parameters

-

dma Where dma is the base address of dma peripheral

- Returns

- None

◆ DMAC_IntFlag()

| __STATIC_INLINE uint32_t DMAC_IntFlag | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| uint32_t | FlgIdx | ||

| ) |

Adjust interrupt event occured or not after masking.

- Parameters

-

dma where dma is the base address of dma peripheral ChIdx where ChIdx is the dma channel number.It could be 0,1,2 FlgIdx where FlgIdx is interrupt type,It could be:Dma interrupt status

- Returns

- None

◆ DMAC_IntFlagMsk()

| __STATIC_INLINE uint32_t DMAC_IntFlagMsk | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| uint32_t | FlgIdx | ||

| ) |

Adjust interrupt mask set or not.

- Parameters

-

dma where dma is the base address of dma peripheral ChIdx where ChIdx is the dma channel number.It could be 0,1,2 FlgIdx where FlgIdx is interrupt type,It could be:Dma interrupt status

- Returns

- None

◆ DMAC_IsChannelValid()

| __STATIC_INLINE uint32_t DMAC_IsChannelValid | ( | DMA_T * | dma, |

| uint32_t | ChIdx | ||

| ) |

Adjust dma channel is busy or not.

- Parameters

-

dma Where dma is the base address of dma peripheral ChIdx Where chidx is the dma channel number.It could be 0,1,2

- Return values

-

0 dma channel invalid 1 dma channel valid

◆ DMAC_ReleaseChannel()

| void DMAC_ReleaseChannel | ( | DMA_T * | dma, |

| uint32_t | ChIdx | ||

| ) |

Release dma channel.

- Parameters

-

dma Where dma is the base address of dma peripheral

ChIdx Where ChIdx is the dma channel number.It could be 0,1,2

- Returns

- None

◆ DMAC_SetChannelConfig()

| void DMAC_SetChannelConfig | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| DMAC_ChannelConfigTypeDef * | Config | ||

| ) |

Set dma channel config,include control register and config register.

- Parameters

-

dma Where dma is the base address of dma peripheral ChIdx Where ChIdx is the dma channel number.It could be 0,1,2 Config Where Config is the config of dma channel. DMAC_ChannelConfigTypeDef

- Returns

- None

◆ DMAC_SetIntFlagMsk()

| void DMAC_SetIntFlagMsk | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| uint32_t | FlgIdx | ||

| ) |

Mask interrupt,interrupt is useless.

- Parameters

-

dma Where dma is the base address of dma peripheral ChIdx Where ChIdx is the dma channel number.It could be 0,1,2 FlgIdx Where FlgIdx is interrupt type,It could be: DMAC_FLAG_INDEX_TFR

DMAC_FLAG_INDEX_BLK

DMAC_FLAG_INDEX_SRCTFR DMAC_FLAG_INDEX_DSTTFR DMAC_FLAG_INDEX_ERR

- Returns

- None

◆ DMAC_StartChannel()

| void DMAC_StartChannel | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| void * | Src, | ||

| void * | Dst, | ||

| uint32_t | Len | ||

| ) |

Start dma channel to transmit.

- Parameters

-

dma Where dma is the base address of dma peripheral ChIdx Where ChIdx is the dma channel number.It could be 0,1,2 Src Where Src is the address of source data:

Dst Where Dst is the address of destination data:

Len Where Len is the block size number:

- Returns

- None

◆ DMAC_StatusFlag()

| __STATIC_INLINE uint32_t DMAC_StatusFlag | ( | DMA_T * | dma, |

| uint32_t | ChIdx, | ||

| uint32_t | FlgIdx | ||

| ) |

Adjust interrupt raw flag set or not.

- Parameters

-

dma where dma is the base address of dma peripheral ChIdx where ChIdx is the dma channel number.It could be 0,1,2 FlgIdx where FlgIdx is interrupt type,It could be:Dma interrupt status

- Returns

- None

◆ DMAC_StopChannel()

| void DMAC_StopChannel | ( | DMA_T * | dma, |

| uint32_t | ChIdx | ||

| ) |

Stop dma channel.

- Parameters

-

dma Where dma is the base address of dma peripheral ChIdx Where ChIdx is the dma channel number.It could be 0,1,2

- Returns

- None