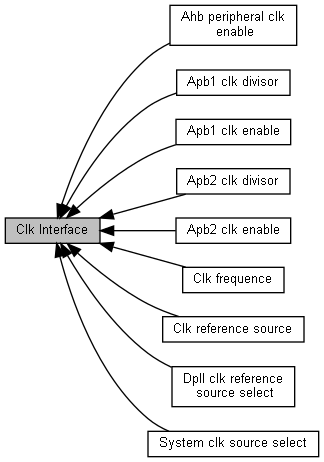

Clk Interface. More...

Modules | |

| Clk frequence | |

| Clk frequence definitions. | |

| System clk source select | |

| System clk source definitions. | |

| Dpll clk reference source select | |

| Dpll clk reference source select definitions. | |

| Apb2 clk divisor | |

| Apb2 clk divisor definitions. | |

| Apb1 clk divisor | |

| Apb1 clk divisor definitions. | |

| Apb1 clk enable | |

| Apb1 clk enable definitions. | |

| Apb2 clk enable | |

| Apb2 clk enable definitions. | |

| Ahb peripheral clk enable | |

| Ahb peripheral clk enable definitions. | |

| Clk reference source | |

| Clk reference source definitions. | |

Macros | |

| #define | CLK_DPLL_OUTPUT_DIV (CLK_DPLL_OUT_96M) |

| #define | CLK_APB1_WDTSEL_MILLI_PULSE (0x00000000UL) |

| #define | CLK_APB1_WDTSEL_RCL32K (0x00010000UL) |

| #define | CLK_APB1_WWDTSEL_MILLI_PULSE (0x00000000UL) |

| #define | CLK_APB1_WWDTSEL_RCL32K (0x00020000UL) |

| #define | CLK_APB1_TMR0SEL_APB1CLK (0x00000000UL) |

| #define | CLK_APB1_TMR0SEL_RCL32K (0x00040000UL) |

| #define | CLK_APB1_TMR0SEL_TM0 (0x00080000UL) |

| #define | CLK_APB2_TMR1SEL_APB2CLK (0x00000000UL) |

| #define | CLK_APB2_TMR1SEL_RCL32K (0x00000100UL) |

| #define | CLK_APB2_TMR1SEL_TM1 (0x00000200UL) |

| #define | CLK_APB2_TMR2SEL_APB2CLK (0x00000000UL) |

| #define | CLK_APB2_TMR2SEL_RCL32K (0x00000400UL) |

| #define | CLK_APB2_TMR2SEL_TM2 (0x00000800UL) |

| #define | CLK_STABLE_STATUS_Pos (24) |

| #define | CLK_STABLE_STATUS_Msk (0x1ul << CLK_STABLE_STATUS_Pos) |

| #define | CLKTRIM_CALC_CLK_SEL_32K (0) |

| #define | CLKTRIM_CALC_CLK_SEL_32M (1) |

| #define | CLKTRIM_CALC_CLK_SEL_EXT (3) |

| #define | CLKTRIM_QDEC_CLK_SEL_APB (0) |

| #define | CLKTRIM_QDEC_CLK_SEL_32K (1) |

| #define | CLKTRIM_KSCAN_CLK_SEL_APB (0) |

| #define | CLKTRIM_KSCAN_CLK_SEL_32K (1) |

| #define | DISABLE_3V_AUTOSYNC ANA->LP_REG_SYNC &= ~ANAC_LP_REG_AUTOSYNC_Msk |

| This macro is used to disable Auto-sync function. More... | |

| #define | ENABLE_3V_AUTOSYNC ANA->LP_REG_SYNC |= ~ANAC_LP_REG_AUTOSYNC_Msk |

| This macro is used to enable Auto-sync function. More... | |

| #define | START_3V_SYNC_NBLOCK ANA->LP_REG_SYNC |= ANAC_LP_REG_SYNC_3V_Msk |

| This macro is used to start sync. More... | |

Enumerations | |

| enum | { CLK_FLASH_CLKDIV_1 = 0x00 , CLK_FLASH_CLKDIV_2 = 0x01 , CLK_FLASH_CLKDIV_4 = 0x02 , CLK_FLASH_CLKDIV_8 = 0x04 , CLK_FLASH_CLKDIV_16 = 0x08 , CLK_FLASH_CLKDIV_32 = 0x10 } |

Functions | |

| __STATIC_INLINE void | CLK_XthStartupConfig (void) |

| Configures the xth clock. More... | |

| __STATIC_INLINE void | CLK_HCLK1Config (uint32_t u32ClkDiv) |

| Configures the Low Speed AHB clock (HCLK). More... | |

| __STATIC_INLINE void | CLK_PCLK1Config (uint32_t u32ClkDiv) |

| Configures the Low Speed APB clock (PCLK1). More... | |

| __STATIC_INLINE void | CLK_PCLK2Config (uint32_t u32ClkDiv) |

| Configures the High Speed APB clock (PCLK2). More... | |

| __STATIC_INLINE void | CLK_SetQdecDiv (uint32_t div) |

| This function used to set qdec divisor. More... | |

| __STATIC_INLINE uint32_t | CLK_GetQdecDiv (void) |

| This function used to get qdec divisor. More... | |

| __STATIC_INLINE void | CLK_SetQdecClkSrc (uint32_t src) |

| This function used to set qdec clk source. More... | |

| __STATIC_INLINE void | CLK_SetKeyscanDiv (uint32_t div) |

| This function used to set keyscan divisor. More... | |

| __STATIC_INLINE uint32_t | CLK_GetKeyscanDiv (void) |

| This function used to get keyscan divisor. More... | |

| __STATIC_INLINE void | CLK_SetKeyscanClkSrc (uint32_t src) |

| This function used to set keyscan clk source. More... | |

| __STATIC_INLINE void | CLK_SetDpllOutputFreq (uint32_t freq) |

| This function set DPLL frequence. More... | |

| __STATIC_INLINE void | CLK_SetTemperatureGain (uint32_t gain) |

| This function set temperature gain value. More... | |

| __STATIC_INLINE void | CLK_EnableTempDetect (void) |

| This function set temperature function enable. More... | |

| __STATIC_INLINE void | CLK_EnableClkTrim (FunctionalState NewState) |

| This function used to enable clktrim peripheral. More... | |

| __STATIC_INLINE void | CLK_EnableClkTrimCalc (FunctionalState NewState) |

| This function used to enable clktrim calculate function. More... | |

| __STATIC_INLINE void | CLK_SelectClkTrimSrc (uint32_t src) |

| This function used to select calculate clk source. More... | |

| __STATIC_INLINE void | CLK_SetClkTrimCalClkDiv (uint16_t div) |

| This function is used to set calculated high speed clock source (HSCK = RCH/EXT_CLK) divisor of CLKTRIM. More... | |

| __STATIC_FORCEINLINE void | CLK_SetFlashClkDiv (uint8_t div) |

| This function is used to set flash clk divisor. More... | |

| uint32_t | CLK_GetHCLKFreq (void) |

| This function get HCLK frequency. The frequency unit is Hz. More... | |

| uint32_t | CLK_GetCPUFreq (void) |

| This function get CPU frequency. The frequency unit is Hz. More... | |

| uint32_t | CLK_GetPCLK1Freq (void) |

| This function get APB1 frequency. The frequency unit is Hz. More... | |

| uint32_t | CLK_GetPCLK2Freq (void) |

| This function get APB2 frequency. The frequency unit is Hz. More... | |

| void | CLK_RefClkSrcConfig (uint32_t u32ClkSrc) |

| This function set 16M ref clock source. More... | |

| void | CLK_SYSCLKConfig (uint32_t u32ClkSrc, uint32_t freq_out) |

| This function set HCLK clock source. More... | |

| void | CLK_HCLKConfig (uint32_t u32ClkDiv) |

| This function set CPU frequency divider. The frequency unit is Hz. More... | |

| void | CLK_AHBPeriphClockCmd (uint32_t CLK_AHBPeriph, FunctionalState NewState) |

| Enables or disables the AHB peripheral clock. More... | |

| void | CLK_APB1PeriphClockCmd (uint32_t CLK_APB1Periph, FunctionalState NewState) |

| Enables or disables the Low Speed APB (APB1) peripheral clock. More... | |

| void | CLK_APB2PeriphClockCmd (uint32_t CLK_APB2Periph, FunctionalState NewState) |

| Enables or disables the High Speed APB (APB2) peripheral clock. More... | |

| uint32_t | CLK_WaitClockReady (uint32_t u32ClkMask) |

| This function check selected clock source status. More... | |

| uint32_t | CLK_Wait3vSyncReady (void) |

| This function wait sync 3v clock locale stable. More... | |

| void | CLK_Set3vSyncAuto (void) |

| This function wait sync 3v clock locale stable by hardware. More... | |

| void | CLK_SetWdtClkSrc (uint32_t u32clksel) |

| This API is used to select wdt clock source. More... | |

| void | CLK_SetWwdtClkSrc (uint32_t u32clksel) |

| This API is used to select wwdt clock source. More... | |

| void | CLK_SetTmrClkSrc (TIMER_T *timer, uint32_t u32clksel) |

| This API is used to SELECT timer clock source. More... | |

| uint32_t | CLK_GetPeripheralFreq (void *Peripheral) |

| This API is used to get peripheral clk frequence. More... | |

Detailed Description

Clk Interface.

Macro Definition Documentation

◆ CLK_APB1_TMR0SEL_APB1CLK

| #define CLK_APB1_TMR0SEL_APB1CLK (0x00000000UL) |

Timer0 clk source select apb_clk / 2048

◆ CLK_APB1_TMR0SEL_RCL32K

| #define CLK_APB1_TMR0SEL_RCL32K (0x00040000UL) |

Timer0 clk source select rcl 32k

◆ CLK_APB1_TMR0SEL_TM0

| #define CLK_APB1_TMR0SEL_TM0 (0x00080000UL) |

Timer0 clk source select externel input

◆ CLK_APB1_WDTSEL_MILLI_PULSE

| #define CLK_APB1_WDTSEL_MILLI_PULSE (0x00000000UL) |

Wdt clk source select apb_clk / 2048

◆ CLK_APB1_WDTSEL_RCL32K

| #define CLK_APB1_WDTSEL_RCL32K (0x00010000UL) |

Wdt clk source select rcl 32k

◆ CLK_APB1_WWDTSEL_MILLI_PULSE

| #define CLK_APB1_WWDTSEL_MILLI_PULSE (0x00000000UL) |

Wwdt clk source select apb_clk / 2048

◆ CLK_APB1_WWDTSEL_RCL32K

| #define CLK_APB1_WWDTSEL_RCL32K (0x00020000UL) |

Wwdt clk source select rcl 32k

◆ CLK_APB2_TMR1SEL_APB2CLK

| #define CLK_APB2_TMR1SEL_APB2CLK (0x00000000UL) |

Timer1 clk source select apb_clk / 2048

◆ CLK_APB2_TMR1SEL_RCL32K

| #define CLK_APB2_TMR1SEL_RCL32K (0x00000100UL) |

Timer1 clk source select rcl 32k

◆ CLK_APB2_TMR1SEL_TM1

| #define CLK_APB2_TMR1SEL_TM1 (0x00000200UL) |

Timer1 clk source select externel input

◆ CLK_APB2_TMR2SEL_APB2CLK

| #define CLK_APB2_TMR2SEL_APB2CLK (0x00000000UL) |

Timer2 clk source select apb_clk / 2048

◆ CLK_APB2_TMR2SEL_RCL32K

| #define CLK_APB2_TMR2SEL_RCL32K (0x00000400UL) |

Timer2 clk source select rcl 32k

◆ CLK_APB2_TMR2SEL_TM2

| #define CLK_APB2_TMR2SEL_TM2 (0x00000800UL) |

Timer2 clk source select externel input

◆ CLK_DPLL_OUTPUT_DIV

| #define CLK_DPLL_OUTPUT_DIV (CLK_DPLL_OUT_96M) |

Clk dpll output

◆ CLK_STABLE_STATUS_Msk

| #define CLK_STABLE_STATUS_Msk (0x1ul << CLK_STABLE_STATUS_Pos) |

Clk stable register mask value

◆ CLK_STABLE_STATUS_Pos

| #define CLK_STABLE_STATUS_Pos (24) |

Clk stable register position

◆ CLKTRIM_CALC_CLK_SEL_32K

| #define CLKTRIM_CALC_CLK_SEL_32K (0) |

Clktrim calibrate source selecet 32K

◆ CLKTRIM_CALC_CLK_SEL_32M

| #define CLKTRIM_CALC_CLK_SEL_32M (1) |

Clktrim calibrate source selecet 32M

◆ CLKTRIM_CALC_CLK_SEL_EXT

| #define CLKTRIM_CALC_CLK_SEL_EXT (3) |

Clktrim calibrate source selecet external clk

◆ CLKTRIM_KSCAN_CLK_SEL_32K

| #define CLKTRIM_KSCAN_CLK_SEL_32K (1) |

Kscan clk source selecet 32K

◆ CLKTRIM_KSCAN_CLK_SEL_APB

| #define CLKTRIM_KSCAN_CLK_SEL_APB (0) |

Kscan clk source selecet apb clk

◆ CLKTRIM_QDEC_CLK_SEL_32K

| #define CLKTRIM_QDEC_CLK_SEL_32K (1) |

Qdec clk source selecet 32K

◆ CLKTRIM_QDEC_CLK_SEL_APB

| #define CLKTRIM_QDEC_CLK_SEL_APB (0) |

Qdec clk source selecet apb clk

◆ DISABLE_3V_AUTOSYNC

| #define DISABLE_3V_AUTOSYNC ANA->LP_REG_SYNC &= ~ANAC_LP_REG_AUTOSYNC_Msk |

This macro is used to disable Auto-sync function.

- Returns

- none

◆ ENABLE_3V_AUTOSYNC

| #define ENABLE_3V_AUTOSYNC ANA->LP_REG_SYNC |= ~ANAC_LP_REG_AUTOSYNC_Msk |

This macro is used to enable Auto-sync function.

- Returns

- none

◆ START_3V_SYNC_NBLOCK

| #define START_3V_SYNC_NBLOCK ANA->LP_REG_SYNC |= ANAC_LP_REG_SYNC_3V_Msk |

This macro is used to start sync.

- Returns

- none

Enumeration Type Documentation

◆ anonymous enum

| anonymous enum |

Function Documentation

◆ CLK_AHBPeriphClockCmd()

| void CLK_AHBPeriphClockCmd | ( | uint32_t | CLK_AHBPeriph, |

| FunctionalState | NewState | ||

| ) |

Enables or disables the AHB peripheral clock.

- Note

- After reset, the peripheral clock (used for registers read/write access) is disabled and the application software has to enable this clock before using it.

- Parameters

-

CLK_AHBPeriph specifies the AHB2 peripheral to gates its clock. This parameter can be any combination of the following values: Ahb peripheral clk enable NewState : new state of the specified peripheral clock. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

◆ CLK_APB1PeriphClockCmd()

| void CLK_APB1PeriphClockCmd | ( | uint32_t | CLK_APB1Periph, |

| FunctionalState | NewState | ||

| ) |

Enables or disables the Low Speed APB (APB1) peripheral clock.

- Note

- After reset, the peripheral clock (used for registers read/write access) is disabled and the application software has to enable this clock before using it.

- Parameters

-

CLK_APB1Periph specifies the APB1 peripheral to gates its clock. This parameter can be any combination of the following values: Apb1 clk enable NewState : new state of the specified peripheral clock. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

◆ CLK_APB2PeriphClockCmd()

| void CLK_APB2PeriphClockCmd | ( | uint32_t | CLK_APB2Periph, |

| FunctionalState | NewState | ||

| ) |

Enables or disables the High Speed APB (APB2) peripheral clock.

- Note

- After reset, the peripheral clock (used for registers read/write access) is disabled and the application software has to enable this clock before using it.

- Parameters

-

CLK_APB2Periph specifies the APB2 peripheral to gates its clock. This parameter can be any combination of the following values: Apb2 clk enable NewState new state of the specified peripheral clock. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

◆ CLK_EnableClkTrim()

| __STATIC_INLINE void CLK_EnableClkTrim | ( | FunctionalState | NewState | ) |

This function used to enable clktrim peripheral.

- Parameters

-

[in] NewState new state of the clk.This parameter can be: ENABLE or DISABLE.

- Returns

- none

◆ CLK_EnableClkTrimCalc()

| __STATIC_INLINE void CLK_EnableClkTrimCalc | ( | FunctionalState | NewState | ) |

This function used to enable clktrim calculate function.

- Parameters

-

[in] NewState new state of the clk.This parameter can be: ENABLE or DISABLE.

- Returns

- none

◆ CLK_EnableTempDetect()

| __STATIC_INLINE void CLK_EnableTempDetect | ( | void | ) |

This function set temperature function enable.

- Returns

- none

◆ CLK_GetCPUFreq()

| uint32_t CLK_GetCPUFreq | ( | void | ) |

This function get CPU frequency. The frequency unit is Hz.

- Returns

- CPU frequency

◆ CLK_GetHCLKFreq()

| uint32_t CLK_GetHCLKFreq | ( | void | ) |

This function get HCLK frequency. The frequency unit is Hz.

- Returns

- HCLK frequency

◆ CLK_GetKeyscanDiv()

| __STATIC_INLINE uint32_t CLK_GetKeyscanDiv | ( | void | ) |

This function used to get keyscan divisor.

- Returns

- kscan divisor value

◆ CLK_GetPCLK1Freq()

| uint32_t CLK_GetPCLK1Freq | ( | void | ) |

This function get APB1 frequency. The frequency unit is Hz.

- Returns

- HCLK frequency

◆ CLK_GetPCLK2Freq()

| uint32_t CLK_GetPCLK2Freq | ( | void | ) |

This function get APB2 frequency. The frequency unit is Hz.

- Returns

- HCLK frequency

◆ CLK_GetPeripheralFreq()

| uint32_t CLK_GetPeripheralFreq | ( | void * | Peripheral | ) |

This API is used to get peripheral clk frequence.

- Parameters

-

[in] Peripheral The base address of peripheral module

- Returns

- none

- Note

- This API is only used to select timer clock source

◆ CLK_GetQdecDiv()

| __STATIC_INLINE uint32_t CLK_GetQdecDiv | ( | void | ) |

This function used to get qdec divisor.

- Returns

- qdec divisor value

◆ CLK_HCLK1Config()

| __STATIC_INLINE void CLK_HCLK1Config | ( | uint32_t | u32ClkDiv | ) |

Configures the Low Speed AHB clock (HCLK).

- Parameters

-

u32ClkDiv defines the AHB clock divisor. This clock is derived from the AHB clock (HCLK). This parameter can be 0~15,hclk = hclk / (u32ClkDiv + 1):

- Returns

- None

◆ CLK_HCLKConfig()

| void CLK_HCLKConfig | ( | uint32_t | u32ClkDiv | ) |

This function set CPU frequency divider. The frequency unit is Hz.

- Parameters

-

[in] u32ClkDiv is ahb clock division

- Returns

- HCLK frequency

◆ CLK_PCLK1Config()

| void CLK_PCLK1Config | ( | uint32_t | u32ClkDiv | ) |

Configures the Low Speed APB clock (PCLK1).

This function set APB1 frequency divider. The frequency unit is Hz.

- Parameters

-

u32ClkDiv defines the APB1 clock divisor. This clock is derived from the AHB clock (HCLK). This parameter can be 0~15,PCLK1 = hclk / (u32ClkDiv * 2):

- Returns

- None

- Parameters

-

[in] u32ClkDiv is is APB1 clock division

- Returns

- HCLK frequency

◆ CLK_PCLK2Config()

| void CLK_PCLK2Config | ( | uint32_t | u32ClkDiv | ) |

Configures the High Speed APB clock (PCLK2).

This function set APB2 frequency divider. The frequency unit is Hz.

- Parameters

-

u32ClkDiv defines the APB2 clock divisor. This clock is derived from the AHB clock (HCLK). This parameter can be 0~15,PCLK2 = hclk / (u32ClkDiv * 2):

- Returns

- None

- Parameters

-

[in] u32ClkDiv is is APB2 clock division

- Returns

- HCLK frequency

◆ CLK_RefClkSrcConfig()

| void CLK_RefClkSrcConfig | ( | uint32_t | u32ClkSrc | ) |

This function set 16M ref clock source.

- Parameters

-

[in] u32ClkSrc is HCLK clock source. Including :

- Returns

- None

◆ CLK_SelectClkTrimSrc()

| __STATIC_INLINE void CLK_SelectClkTrimSrc | ( | uint32_t | src | ) |

This function used to select calculate clk source.

- Parameters

-

[in] src clk source, including: CLKTRIM_CALC_CLK_SEL_32K CLKTRIM_CALC_CLK_SEL_32M CLKTRIM_CALC_CLK_SEL_EXT

- Returns

- none

◆ CLK_Set3vSyncAuto()

| void CLK_Set3vSyncAuto | ( | void | ) |

This function wait sync 3v clock locale stable by hardware.

- Returns

- none

◆ CLK_SetClkTrimCalClkDiv()

| __STATIC_INLINE void CLK_SetClkTrimCalClkDiv | ( | uint16_t | div | ) |

This function is used to set calculated high speed clock source (HSCK = RCH/EXT_CLK) divisor of CLKTRIM.

- Parameters

-

[in] div clock divisor (9 bits), 0: No division, cal_clk = HSCK others: Divided by 2*div, cal_clk = HSCK / (2*div)

- Returns

- none

◆ CLK_SetDpllOutputFreq()

| __STATIC_INLINE void CLK_SetDpllOutputFreq | ( | uint32_t | freq | ) |

This function set DPLL frequence.

- Parameters

-

[in] freq is target frequency,it could be: CLK_DPLL_OUT_48M CLK_DPLL_OUT_64M

- Returns

- none

◆ CLK_SetFlashClkDiv()

| __STATIC_FORCEINLINE void CLK_SetFlashClkDiv | ( | uint8_t | div | ) |

This function is used to set flash clk divisor.

- Parameters

-

[in] div clock divisor

- Returns

- none

◆ CLK_SetKeyscanClkSrc()

| __STATIC_INLINE void CLK_SetKeyscanClkSrc | ( | uint32_t | src | ) |

This function used to set keyscan clk source.

- Parameters

-

[in] src is keyscan sclk source,apb or 32k

- Returns

- none

◆ CLK_SetKeyscanDiv()

| __STATIC_INLINE void CLK_SetKeyscanDiv | ( | uint32_t | div | ) |

This function used to set keyscan divisor.

- Parameters

-

[in] div is keyscan sclk dividor ratio,9 bit width

- Returns

- none

◆ CLK_SetQdecClkSrc()

| __STATIC_INLINE void CLK_SetQdecClkSrc | ( | uint32_t | src | ) |

This function used to set qdec clk source.

- Parameters

-

[in] src is qdec sclk source,apb or 32k

- Returns

- none

◆ CLK_SetQdecDiv()

| __STATIC_INLINE void CLK_SetQdecDiv | ( | uint32_t | div | ) |

This function used to set qdec divisor.

- Parameters

-

[in] div is qdec sclk dividor ratio,9 bit width

- Returns

- none

◆ CLK_SetTemperatureGain()

| __STATIC_INLINE void CLK_SetTemperatureGain | ( | uint32_t | gain | ) |

This function set temperature gain value.

- Parameters

-

[in] gain is target gain value

- Returns

- none

◆ CLK_SetTmrClkSrc()

| void CLK_SetTmrClkSrc | ( | TIMER_T * | timer, |

| uint32_t | u32clksel | ||

| ) |

This API is used to SELECT timer clock source.

- Parameters

-

[in] timer The base address of Timer module [in] u32clksel timer clock selection. Could be - CLK_APB_TMR0SEL_APB1CLK, CLK_APB_TMR0SEL_LIRC,CLK_APB_TMR0SEL_TM0

- CLK_APB_TMR1SEL_APB2CLK, CLK_APB_TMR1SEL_LIRC,CLK_APB_TMR0SEL_TM1

- CLK_APB_TMR2SEL_APB2CLK, CLK_APB_TMR2SEL_LIRC,CLK_APB_TMR0SEL_TM2

- Returns

- none

- Note

- This API is only used to select timer clock source

◆ CLK_SetWdtClkSrc()

| void CLK_SetWdtClkSrc | ( | uint32_t | u32clksel | ) |

This API is used to select wdt clock source.

- Parameters

-

[in] u32clksel wdt clock selection. Could be

- Returns

- none

- Note

- This API is only used to select wdt clock source

◆ CLK_SetWwdtClkSrc()

| void CLK_SetWwdtClkSrc | ( | uint32_t | u32clksel | ) |

This API is used to select wwdt clock source.

- Parameters

-

[in] u32clksel wwdt clock selection. Could be

- Returns

- none

- Note

- This API is only used to select wwdt clock source

◆ CLK_SYSCLKConfig()

| void CLK_SYSCLKConfig | ( | uint32_t | u32ClkSrc, |

| uint32_t | freq_out | ||

| ) |

This function set HCLK clock source.

- Parameters

-

[in] u32ClkSrc is HCLK clock source. Including : [in] freq_out is output frequence clock

- Returns

- None

◆ CLK_Wait3vSyncReady()

| uint32_t CLK_Wait3vSyncReady | ( | void | ) |

This function wait sync 3v clock locale stable.

- Parameters

-

[in] none

- Return values

-

0 clock sync is not stable 1 clock sync is stable

To wait for clock ready by specified CLKSTATUS bit or timeout (~5ms)

◆ CLK_WaitClockReady()

| uint32_t CLK_WaitClockReady | ( | uint32_t | u32ClkMask | ) |

This function check selected clock source status.

- Parameters

-

[in] u32ClkMask is selected clock source. Including

- Return values

-

0 clock is not stable 1 clock is stable

To wait for clock ready by specified CLKSTATUS bit or timeout (~5ms)

◆ CLK_XthStartupConfig()

| __STATIC_INLINE void CLK_XthStartupConfig | ( | void | ) |

Configures the xth clock.

- Returns

- None