NDK 低功耗开发指南¶

本文主要通过一些示例,介绍低功耗各个模式、使用的方法以及可能遇到的问题。

1 低功耗模式¶

低功耗模式介绍如下表所示:

模式名称 |

进入 |

唤醒 |

1.2V区时钟 |

时钟 |

1.2V供电 |

|---|---|---|---|---|---|

STANDBY_M0 |

Sleep_mode = 3, Buck_en_ctrl=0, Buck_bp_ctrl=0, Flashldo_bp_en_ctrl =0, Flashldo_lp_en_en_ctrl =0,WFI |

P00,P01,P02,BOD/LVR(可选,需保证慢时钟开启),PIN RESET |

全部关闭 |

全部关闭 |

断电 |

STANDBY_M1 |

Sleep_mode = 2, ldo_pwr_ctrl = 0, ldol_ pwr ctrl = 0/1, cpu pwr ctrl = 0/1, sram0/1 pwr ctrl = 0/1, ll_ram pwr ctrl=0/1, phy_ram pwr _ctrl=0/1, Buck_en_ctrl=0, Buck_bp_ctrl=0, Flashldo_bp_en_ctrl =0, Flashldo_lp_en_en_ctrl =0,WFI |

所有GPIO(边沿去抖),SLPTMR,WDT,BOD/LVR(可选), PIN RESET |

CLK32K, 其他全部关闭 |

慢时钟 |

LPLDOL/H :LL_RAM(可选),PHY_RAM/PHY_REGS(可选),SRAM0/1(可选),decrypt_ram(可选,cpu模块不保电,没办法做到只保少部分寄存器)LPLDOL/H:asnactrl_l(rcc的寄存器)GPIOWDTBOD,LVR |

DEEPSLEEP |

Sleep_mode = 1, ldol_power_ctrl = 0/1, Buck_en_ctrl=0, Buck_bp_ctrl=0, Flashldo_bp_en_ctrl =0/1, Flashldo_lp_en_en_ctrl =1/0,WFI |

所有GPIO,SLPTMR,WDT,TIMER0/1/2,BOD/LVR(可选),PIN RESET |

CLK32K,其他全部关闭 |

慢时钟 |

LPLDOL/H:其他数字模块,LPLDOL/H:WakeupGPIO,WDT,Timer0/1/2,(需要测试,确认如何安全使用) |

SLEEP |

Sleep_mode = 0, WFI |

所有外设中断,BOD/LVR(可选),PIN RESET |

CLK32K,CPU_CLK关闭,RCH、XTH、DPLL根据软件配置选择打开 |

慢时钟快时钟 |

HP_LDO供电 |

2 开发流程¶

2.1 低功耗使用流程¶

2.1.1 Sleep模式¶

进入流程:

配置sleep_mode为sleep模式

唤醒源配置

设置flash dp_en为0

设置CPU SLEEPDEEP寄存器为0;地址:0xE000ED10

考虑安全,建议进行一次手动3V同步操作

__WFI();

退出流程:

唤醒源产生中断;

处理中断,清除中断源;

备注:

支持m0调试模式,不支持riscv调试模式

2.1.2 Deepsleep模式¶

进入流程:

配置sleep_mode为deepsleep模式,配置各电压域的power switch,配置rcl_en_ctrl,xtl_pwr_ctrl,Buck和flashldo的配置建议使用driver默认

Power Switch

模式1(推荐)

模式2

模式3

lpldoh_en

1

1

0

lpldol_en

1

0

1

Ldo_pwr_ctrl

1

1

1

Ldol_pwr_ctrl

0

1

1

Peri_pwr_ctrl(cpu/ll_sram/phy_sram/sram0/sram1)

1(ram可配)

1(ram可配)

1(ram可配)

Lpldoh_iso_en

1(配置0待测试)

0

0

唤醒源配置:所有GPIO,SLPTMR,WDT,TIMER0/1/2,BOD/LVR(可选),PIN RESET。对于模式1,如果Lpldoh_iso_en配置为1,则不支持TIMER0/1/2唤醒;如果Lpldoh_iso_en配置为0,则支持TIMER0/1/2唤醒和PWM输出(需要测试是否有漏电)。对于模式2或者模式3,上述唤醒源都可以唤醒系统。BOD,LVR唤醒需要开启32K时钟。

对于模式1,如果Lpldoh_iso_en配置为1,不支持PWM输出;如果Lpldoh_iso_en配置为0,则支持PWM输出(需要测试是否有漏电)。对于模式2或者模式3, PWM可以输出

Flash dp设置为1,并退出enhance模式。配置合适的dp,和rdp时间

建议cpu地址重映射功能开启,映射地址为ram保电区域,可加快唤醒后,程序执行速度

Dly_time2需要根据测试结果重新配置,默认值比较大

设置CPU SLEEPDEEP寄存器为1;地址:0xE000ED10

Flash控制器退出增强型模式;

考虑安全,建议进行一次手动3V同步操作

_WFI();

退出流程:

唤醒源唤醒,产生lp中断或者唤醒源相对应的中断

清除相应flag

备注:

支持m0调试模式(低功耗期间会丢失),不支持riscv调试模式

gpio唤醒电平,至少需要保持一个完整的32K时钟周期。如果需要读取的gpio的中断,需要7个32K时钟周期(需要dly2的延时决定);如果32K时钟关闭,则唤醒需要的时间更久,和32K时钟的启动时间相关

2.1.3 Standby_m1模式¶

进入流程:

配置sleep_mode为standby_m1模式,配置各电压域的power switch,配置rcl_en_ctrl,xtl_pwr_ctrl,Buck和flashldo的配置建议使用driver默认

模式1(推荐,需测试)

模式2

模式3

lpldoh_en

1

1

0

lpldol_en

1

0

1

Ldo_pwr_ctrl

0

0

0

Ldol_pwr_ctrl

0

1

1

Peri_pwr_ctrl(cpu/ll_sram/phy_sram/sram0/sram1)

1(可配)

1(可配)

1(可配)

Lpldoh_iso_en

1

1

1

唤醒源配置:所有GPIO,SLPTMR,WDT,BOD/LVR(可选),PIN RESET。BOD,LVR唤醒需要开启32K时钟。

flash如果使用4线模式,建议开启dp模式,flash 两线切换四线的时间特别长,一般会有8ms;如果flash使用2线模式,不建议开启dp模式,flash直接掉电处理。

建议cpu地址重映射功能开启,映射地址为ram保电区域,可加快唤醒后,程序执行速度

根据需求,决定是否开启cpu保电功能,寄存器LP_FL_CTRL[4]。可硬件恢复现场,代码实现有特定需求,参见说明部分

Dly_time2需要根据测试结果重新配置,默认值比较大

设置CPU SLEEPDEEP寄存器为1;地址:0xE000ED10

考虑安全,建议进行一次手动3V同步操作

_WFI();

退出流程:

唤醒源唤醒,产生lp中断以及唤醒源相对应的中断

清除相应flag

备注:

不支持m0和riscv调试模式

支持m0的cpu retention功能(现场恢复),不支持riscv的cpu retention功能

gpio唤醒电平,至少需要保持一个完整的32K时钟周期。如果需要读取的gpio的中断,需要7个32K时钟周期(需要dly2的延时决定);如果32K时钟关闭,则唤醒需要的时间更久,和32K时钟的启动时间相关

2.1.4 Standby_m0模式¶

进入流程:

配置sleep_mode为standby_m0模式,配置rcl_en_ctrl,xtl_pwr_ctrl

唤醒源配置:所有P00,P01,P02, BOD/LVR(可选),PIN RESET。

Flash dp设置为0

Dly_time1根据需要决定是否配置,如果不在意m0的唤醒时间不建议去修改。此处的时间测试遍历会比较多,设置的值不好控制

设置CPU SLEEPDEEP寄存器为1;地址:0xE000ED10

考虑安全,建议进行一次手动3V同步操作

_WFI();

退出流程:

唤醒源唤醒,产生lp中断以及唤醒源相对应的中断

清除相应flag

2.3 Standby_m1休眠唤醒¶

以standby m1模式,cpu retention and cpu continue run模式为基础介绍各个时间阶段mcu的动作。

阶段 |

说明 |

时间(us) |

备注 |

|---|---|---|---|

进入休眠 |

从软件发送休眠指令至硬件完全休眠的时间 |

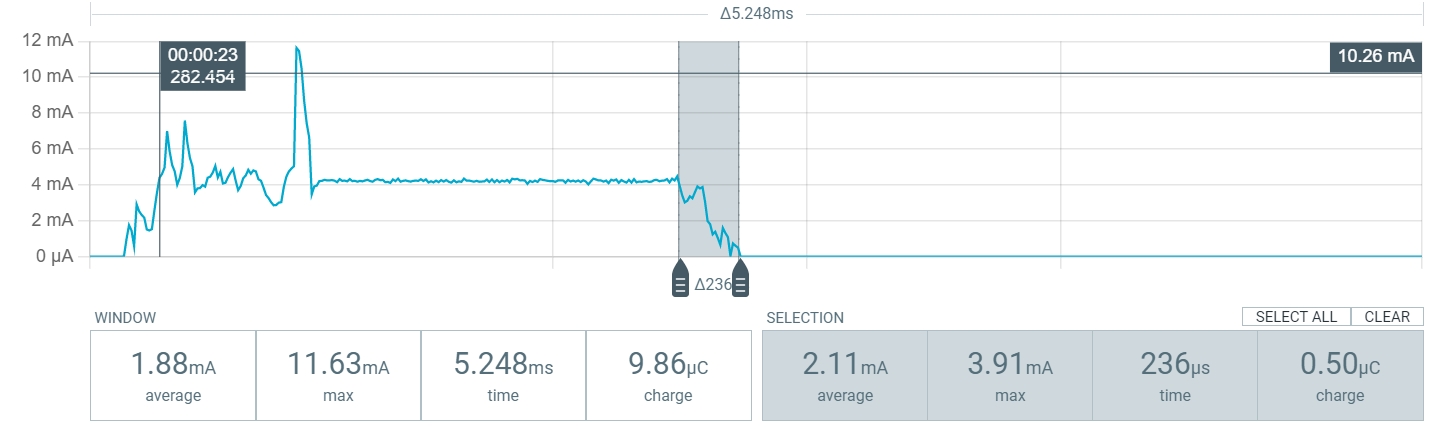

236 |

|

硬件唤醒启动 |

唤醒源触发后硬件完全启动的时间 |

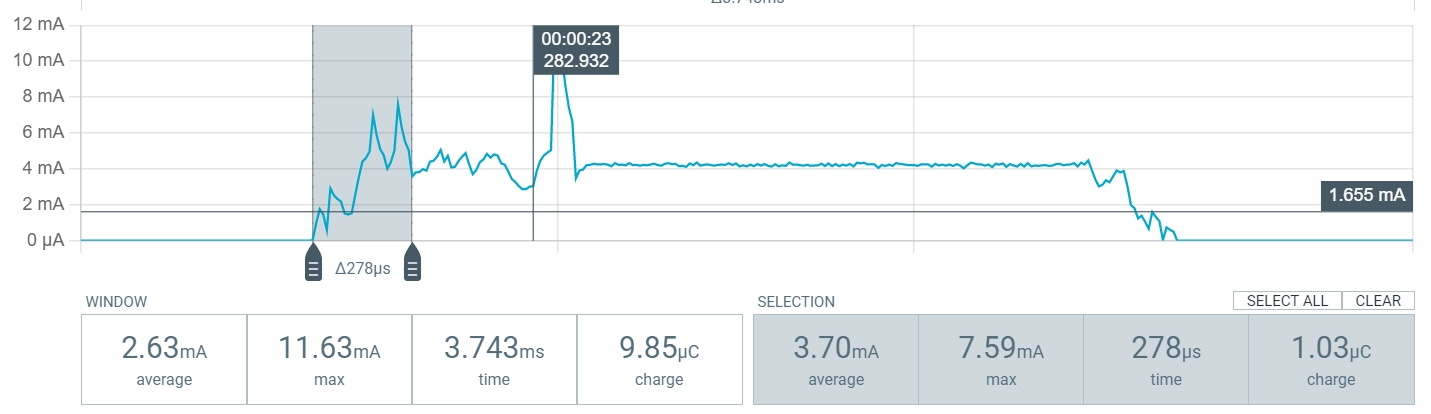

278 |

|

Standby M1 retention模式 |

continue run,唤醒至rx ready时间 |

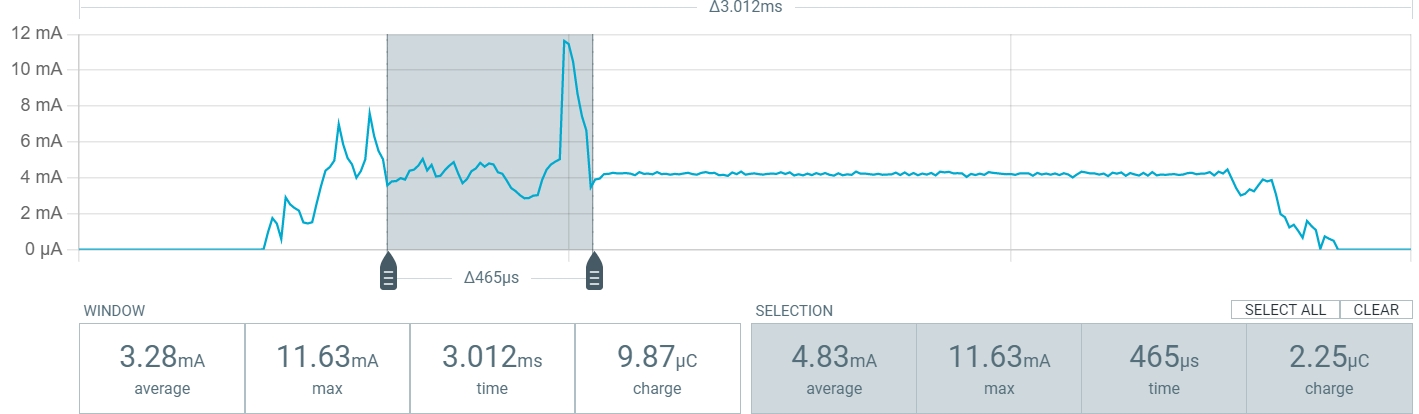

465 |

此模式下软件初始化和RF初始化步骤可以省略 |

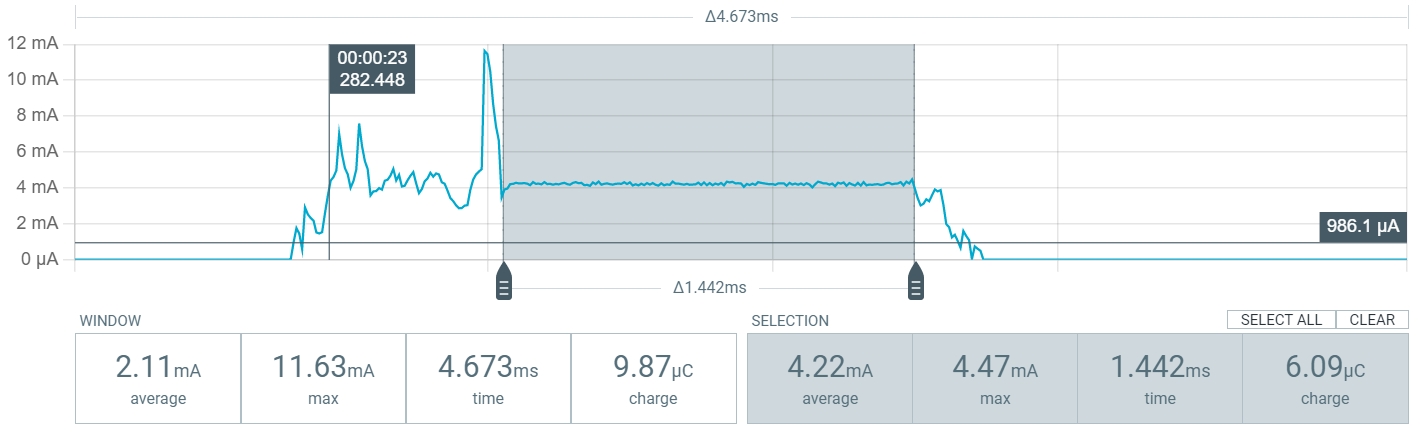

TX/RX(max 59B) |

收发最大payload的时间,根据传输速率与字节数计算得出 |

1888 |

此处按最大数据计算 |

总计 |

休眠唤醒至tx完成/rx完成的时间 |

2867 |

休眠时间

唤醒时间

软件运行至RF ready时间

RF 接收32Byte时间

3 低功耗注意事项¶

如果flash运行在4线enhance模式,进入功耗前需要退出enhance模式。

低功耗模式下供电分两部分LPLDOL和LPLDOH,其中LPLDOL给sram供电,电压范围从0.4~0.9v(未校准芯片有差异),LPLDOH给always on区域部分供电,供电范围0.5~1.2v(未校准芯片有差异),通常在进入低功耗在保证唤醒正常情况下尽量降低两个电压,常温下LPLDOL/H可设置未0/1。

为防止LPLDOH在电源抖动时出现不能唤醒的情况,增加了一个LPLDOH_VREF_TRIM_AON(LP_LPLDO[23:21])控制位,设置值的作用是弥补电源抖动,稳定电压,同时设置完成此值(例如设置为2,LPLDOH电压0.7v)后再想拉低LPLDOH至0.6v是不能完成的,此属于正常现象。

DeepSleep模式下外设timer0/1/2作为唤醒以及PWM在低功耗下输出需要将deepsleep低功耗模式设置为模式2,即dp_mode= LP_DEEPSLEEP_MODE2.

Standby M1 cpu retention模式唤醒后外设部分及RF MAC层寄存器需要重新初始化,PHY、保电的sram、时钟等不需要重新初始化