PAN312x 硬件参考设计¶

1 概述¶

本文档主要介绍 PAN312x芯片方案的硬件原理图设计、PCB 设计建议、静电防护、RF性能等,以及提供一些外围电路的硬件设计方法。

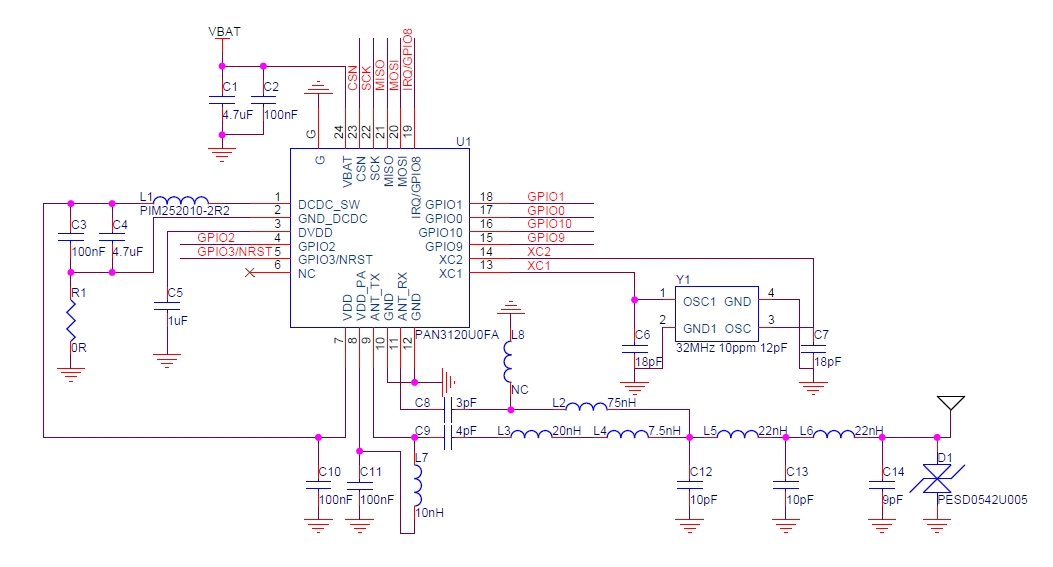

2 典型应用原理图¶

2.3 电源¶

VBAT为芯片电源脚,要求供电能力不小于200mA,供电范围为1.8V–3.6V。

DVDD、VDD、VDD_PA、VBAT等电源相关引脚需要至少预留1个电容,预留一大一小2个电容更佳。

DVDD电容1uF,VDD、VBAT引脚电容不小于4.7μF,应尽可能靠近芯片引脚摆放,电容焊盘和芯片焊盘之间最大距离不超过5mm。

*注:DC-DC ON模式下工作电压范围2V–3.6V

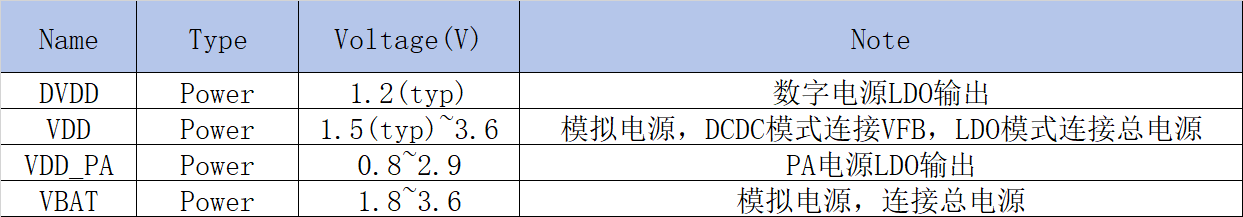

电源引脚描述表¶

2.3.1 DC-DC¶

DC-DC 芯片外围电路

芯片外围电路组成为:L1、C3、C4。

L1推荐型号: PIM252010-2R2MTS00,参数详见章节2.2–典型应用物料清单。选择功率电感,2.2μH,额定电流不小于800mA,DCR不超过80mΩ,未满足要求在DC-DC模式可能会造成RF功能异常。

DCR过大会影响BUCK效率,能量会转化成热量损耗掉,DC-DC输出的驱动电流是有限的,效率越低,能够供给到芯片的有效能量就越少。

DC-DC的两种工作模式:

开启DC-DC模式可以降低系统功耗。

开启LDO(Bypass)模式后芯片内部将VBAT连接到DCDC_SW,这时DCDC_SW处的2.2uH电感作用为一段导体,可以用0Ω电阻替换。

DC-DC、LDO两种模式不能同时开启。

在不考虑功耗的前提下,可将VDD直接连接到VBAT,此时应将电源模式设置为LDO模式。

DC-DC相关引脚说明:

VBAT为DC-DC的供电引脚。

DCDC_SW为DC-DC的功率开关(P-MOS)漏极输出引脚,功率电感应靠近该引脚放置。

VDD为DC-DC的反馈引脚,电容应靠近该引脚放置。

GND_DCDC为DC-DC电源的GND引脚。

*注:DC/DC转换器仅支持对低功率PA电路提供电源,用户选择用高功率PA时,需要用外部电源供电。

2.3.2 DVDD¶

DVDD需要放置1uF电容。 电容最大不应超过1uF,否则会影响芯片正常启动,电容应靠近该引脚放置。

2.4 晶振¶

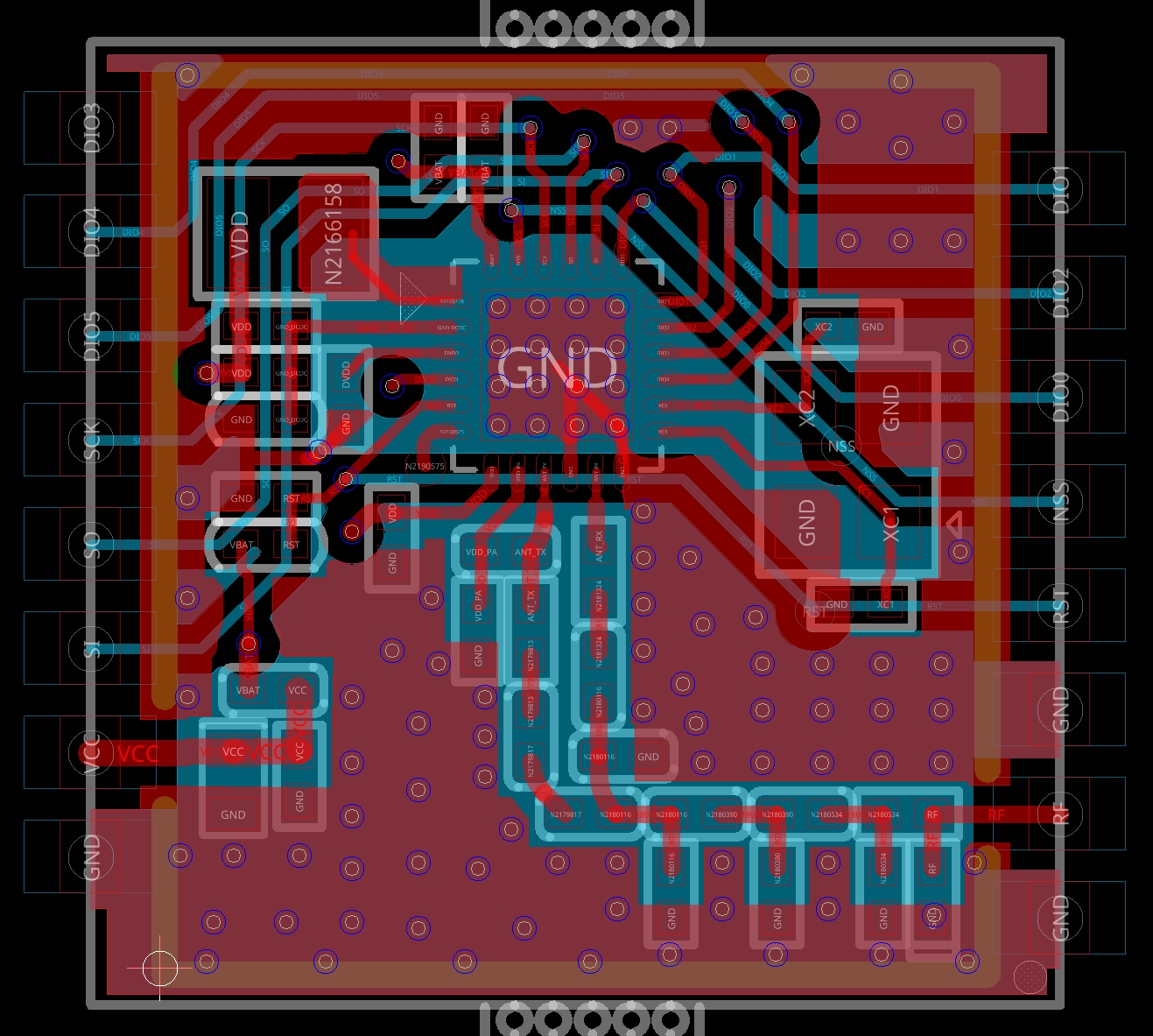

3 PCB设计建议¶

3.1 板材选择和特殊说明¶

关于PCB设计,建议使用四层板,四层板安规特性更好,如需考虑成本等因素,使用两层板布局,需要将中间的EPAD通过顶层GND脚接到外面的大地上,同时中间的EPAD接地过孔尽可能多,比如16个。

芯片下面的PCB板的Bottom层不要走线,特别是靠近射频匹配电路的部分,完整的地平面能保证射频性能。

PCB layout 布局¶

*线宽推荐如下:

板材属性 |

参数 |

|---|---|

PCB板材 |

FR4 |

PCB板厚 |

1.6mm |

50欧姆RF线宽 |

20mil |

接地铺铜与RF走线间距 |

5mil |

3.2 DC/DC layout说明¶

GND_DCDC需要通过0Ω电阻与PCB地单点连接,不要与PCB地直接相接。

DCDC_SW管脚与电感距离尽量短且走线尽量粗,提升DCDC的效率。

DC/DC电感底部需要净空,电容靠近电感放置。

3.3 电源和地 layout说明¶

电源线宽度要求能达到0.5mm以上,承受200毫安的瞬态电流。在靠近芯片电源引脚放置去耦电容,其中小容值电容摆放在更靠近芯片引脚的位置,以便较好地滤除高频噪声。

电源线和地线采用放射状的连接方式,单点接电源/地并且单独走线,RF芯片的电源/地线走线与其它芯片或器件分开来,从总参考电源/地线单独引线,防止受到干扰。如果是从LDO或者DCDC等器件引出电源线,也需要单独引线并且做好滤波措施。芯片底部的GND引脚需要和电路板顶层的GND平面直接相连。

覆地的地线也建议与噪声较少的地线或者总参考地线连接,不与强信号或者强干扰器件地线电源线相连,可以有效地减少整个印制板的工作噪声。

3.4 晶振 layout说明¶

在面积允许的程度下,晶体跟芯片之间保持一定的距离,做好隔热处理。

直插的晶振的焊盘需要保证外径与内径差值有0.2mm以上。

为防止晶振信号干扰到射频信号,印制板上在晶振焊盘和走线的两边需要做覆地处理。

为避免晶振受到天线的发射功率干扰,印制板上的天线部分与晶振焊盘走线部分之间要用0.5mm以上地线作为间隔带,同时晶振的外壳需要离天线3mm以上。

3.5 控制线 layout说明¶

控制类的SPI线、IRQ线需要减少走线干扰,布线时走线较短并且走线两边有完整的覆地。

3.6 射频走线layout说明¶

射频匹配链路按照50Ω阻抗走线(与周边铺地间距0.3mm,背面完整的参考地),可以参考TOP和BOTTOM层的GND平面,RF走线尽可能短,RF线与焊盘宽度一致。

RF线有完整的参考地,从IC端出来就进行包地处理,两边打GND过孔,底层地平面尽量宽,可以使得发射能量较多地从天线端出去。

禁止射频线打过孔换层。

天线旁边的GND可以预留露铜,方便焊接调试天线。

芯片底部多打过孔,QFN封装则打在E-PAD上。

晶振应远离天线,TOP层挖空,周围包地,降低对电源和RF的干扰。

天线辐射区域不要摆放金属器件,净空区挖空处理。

4 RF基本性能¶

4.1 433M频段模组性能¶

编号 |

Frequency(MHz) |

Symbolrate(kbps) |

Power(dBm) |

EVM(%) |

Carr ofst(KHz) |

Dev(KHz) |

|---|---|---|---|---|---|---|

PAN3120MOD_433M |

425 |

500 |

20.9 |

1.9% |

-1.1 |

248 |

PAN3120MOD_433M |

433 |

500 |

21.0 |

1.8% |

0.8 |

252 |

PAN3120MOD_433M |

450 |

500 |

20.1 |

2.8% |

1.4 |

256 |

编号 |

Frequency(MHz) |

IF(kbps) |

Symbolrate(kbps) |

Sen_LDO(dBm) |

Sen_DCDC(dBm) |

|---|---|---|---|---|---|

PAN3120MOD_433M |

430.2 |

500 |

50 |

-109 |

-107 |

PAN3120MOD_433M |

449.3 |

500 |

50 |

-108 |

-107 |

PAN3120MOD_433M |

430.2 |

500 |

9.6 |

-118 |

-116 |

PAN3120MOD_433M |

449.3 |

500 |

9.6 |

-118 |

-116 |

4.2 490M频段模组性能¶

编号 |

Frequency(MHz) |

Symbolrate(kbps) |

Power(dBm) |

EVM(%) |

Carr ofst(KHz) |

Dev(KHz) |

|---|---|---|---|---|---|---|

PAN3120MOD_490M |

470 |

500 |

20.3 |

2.7% |

1.2 |

254 |

PAN3120MOD_490M |

490 |

500 |

20.8 |

2.6% |

-1.4 |

248 |

PAN3120MOD_490M |

510 |

500 |

19.7 |

3.9% |

-1.1 |

250 |

编号 |

Frequency(MHz) |

IF(kbps) |

Symbolrate(kbps) |

Sen_LDO(dBm) |

Sen_DCDC(dBm) |

|---|---|---|---|---|---|

PAN3120MOD_490M |

471 |

500 |

50 |

-109 |

-109 |

PAN3120MOD_490M |

493 |

500 |

50 |

-108 |

-107 |

PAN3120MOD_490M |

509 |

500 |

50 |

-108 |

-106 |

PAN3120MOD_490M |

471 |

500 |

9.6 |

-118 |

-117 |

PAN3120MOD_490M |

493 |

500 |

9.6 |

-118 |

-117 |

PAN3120MOD_490M |

509 |

500 |

9.6 |

-117 |

-117 |