硬件设计参考¶

1. 原理图设计要求¶

1.1 电源设计要求¶

PAN3029 典型供电电压为 3.3V ,芯片有两种工作模式,可以通过配置芯片的工作模式来选 择 LDO 模式和 DC-DC 模式。DC-DC 模式要求供电电压范围为 2-3.6V,LDO 模式要求供电电压 范围为 1.8-3.6V 。下表列出了芯片电源相关的管脚的连接方式和推荐的外接器件值。

芯片内部写 eFuse 的电压范围是 2.25V 到 2.75V ,典型值为 2.5V ,因此在写 eFuse 操作时, 建议外部 VDD1 供电 2.5V 电压。读 eFuse 操作时,电源电压支持到 1.83-3.6V。

PIN序号 |

符号 |

功能 |

DCDC模式 |

非DCDC模式 |

外接器件值 |

|---|---|---|---|---|---|

2 |

DCDC_V_FB |

DCDC 输出 |

- |

- |

2.2uH+1uF+0. 1uF |

6 |

DVDD |

数字电源 LDO 输出 |

- |

- |

1uF |

7 |

VDD123 |

模拟电源 |

DCDC_V_FB |

VCC |

0. 1uF |

8 |

VBAT |

模拟电源 |

VCC |

VCC |

10uF+0. 1uF |

9 |

VDDPA |

PALDO 输出 |

- |

- |

0. 1uF+100pF |

27 |

VBAT_IO |

数字电源 |

VCC |

VCC |

0. 1uF |

28 |

VBAT_DCDC |

DCDC 电源 |

VCC |

VCC |

0. 1uF |

备注: DCDC 模式,管脚 DCDC_V_FB 外接的电感和电容值请严格按照要求的 2.2uH+10uF+0. 1uF 设计,如果电感和电容值小了,会导致芯片功耗上升。

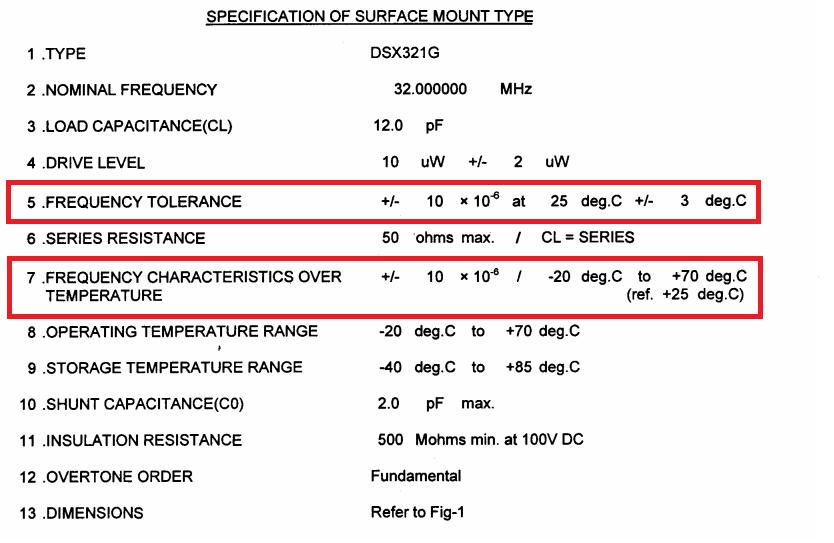

1.2 晶体设计要求¶

对于外部无源晶体的常规要求如下:

1 、晶体频率 32MHz;

2 、ESR 小于 50ohm;

3 、晶体负载电容推荐使用 12pF ,负载电容变化,原理图的晶体并联到地电容要改变;

4 、晶体频率误差 ≤ ±10ppm;

5 、晶振的频率温度(-20~70 °C)特征 ≤ ±10ppm;

6 、激励功率 ≤ 100uW。

推荐用KDS 无源晶体 1C232000AA0B ,具体的参数指标如下所示。

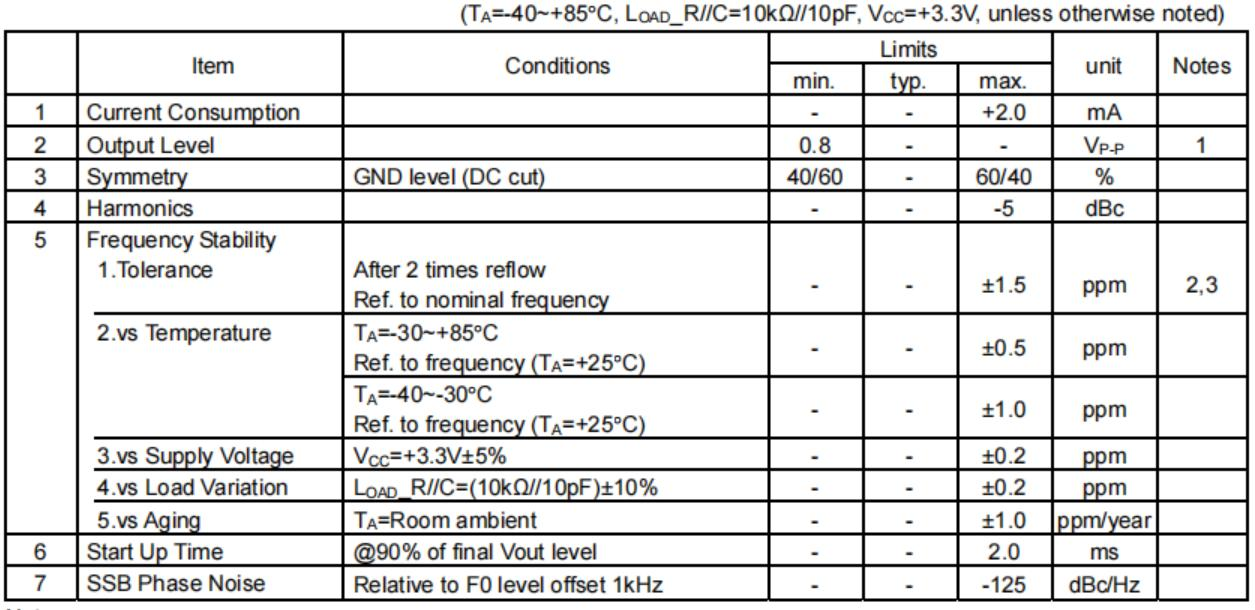

有源晶振的输出直接接到芯片 XC2 管脚,有源晶振的供电可以用芯片的 GPIO 来提供或者 外部电源供电,要求有源晶振支持的工作电压范围为 1.8~3.6V。温度范围-40~85 °C 的应用,推 荐使用 KDS 的有源温补晶体 1XXD32000MBA ,具体的参数如下表所示。

在大发射功率的条件下,芯片会产生大量的热量,这些热量会通过 PCB 传导到晶体,由于 晶体的频率会随着温度产生变化,导致在发射过程中会出现频率漂移,这个漂移会对接收解调产 生较大的挑战,严重的话导致出现接收解调数据错误,出现丢包的现象。不同的 BW 和不同 SF, 对晶体的要求不一样,具体请参考“PAN3029 晶体选型说明文档 ”。

1.3 DCDC设计要求¶

电 感 选 型 要 求 导 通 电 阻 小 于 100 m Ω , 峰 值 电 流 大 于 150mA ( 参 考 型 号 :PIM252010-2R2MTS00)。

1.4 数字接口设计要求¶

1 、SPI 采用 4 线 CSN,SCK,MOSI 和 MISO 接口,最高速率要求低于 10Mbps,操作 efuse 时,不能超过 8Mbps;

2 、I2C 跟 SPI 复用管脚,SCL 复用 SPI 的 SCK,SDA 复用 SPI 的 MOSI,使用 I2C 时 CSN 要 拉高,I2C 的最高速率要求低于 15Mbps;

3 、中断 IRQ ,默认是低电平输出,在发射和接收成功时会输出高电平。

4 、关于 GPIO 的功能配置请参考用户手册,重点提到的是 GPIO11 可以复用为 CAD 检测功 能引脚,GPIO10 可以配置为外部 PA 控制引脚。

1.5 射频前端设计要求¶

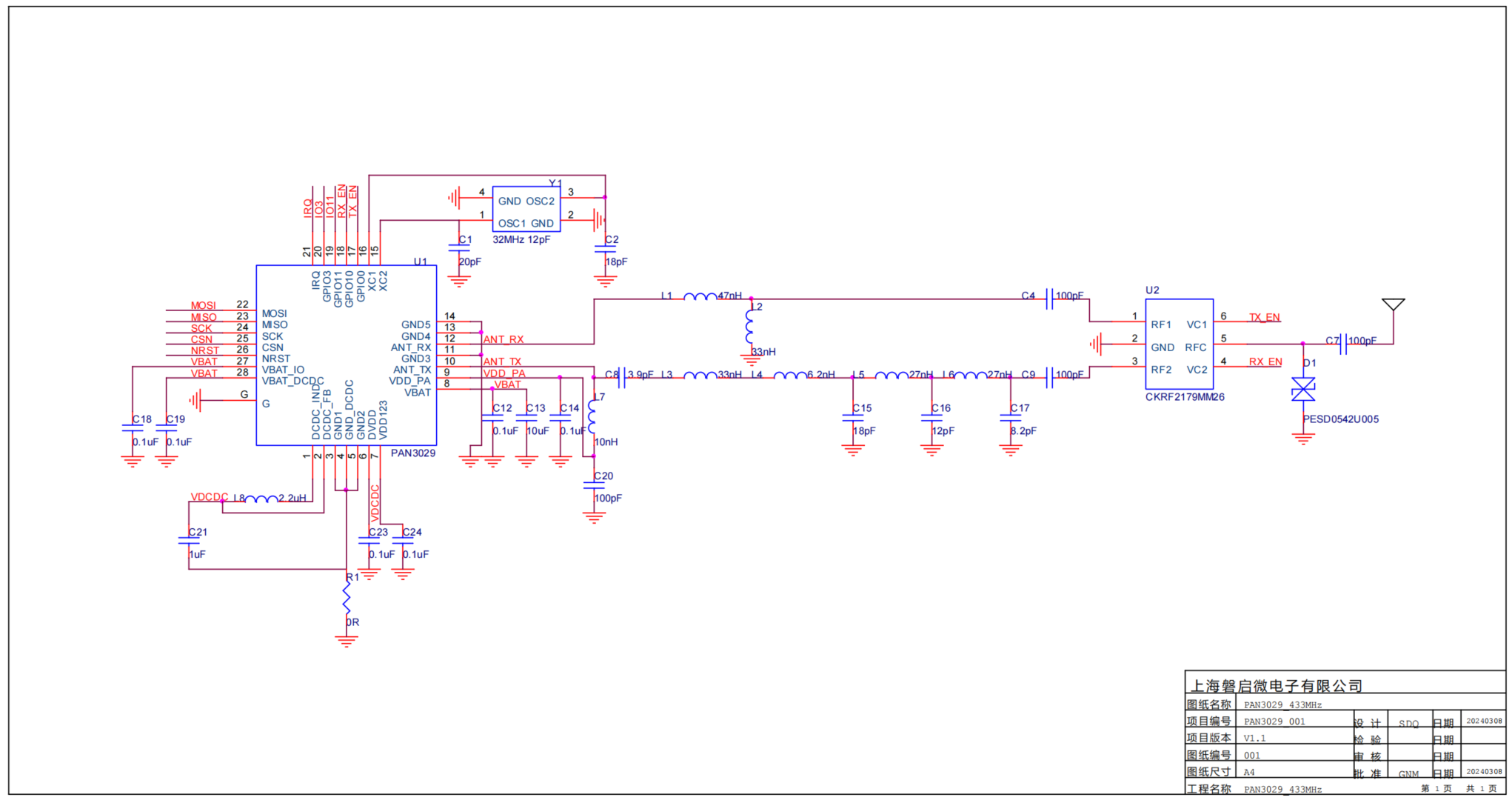

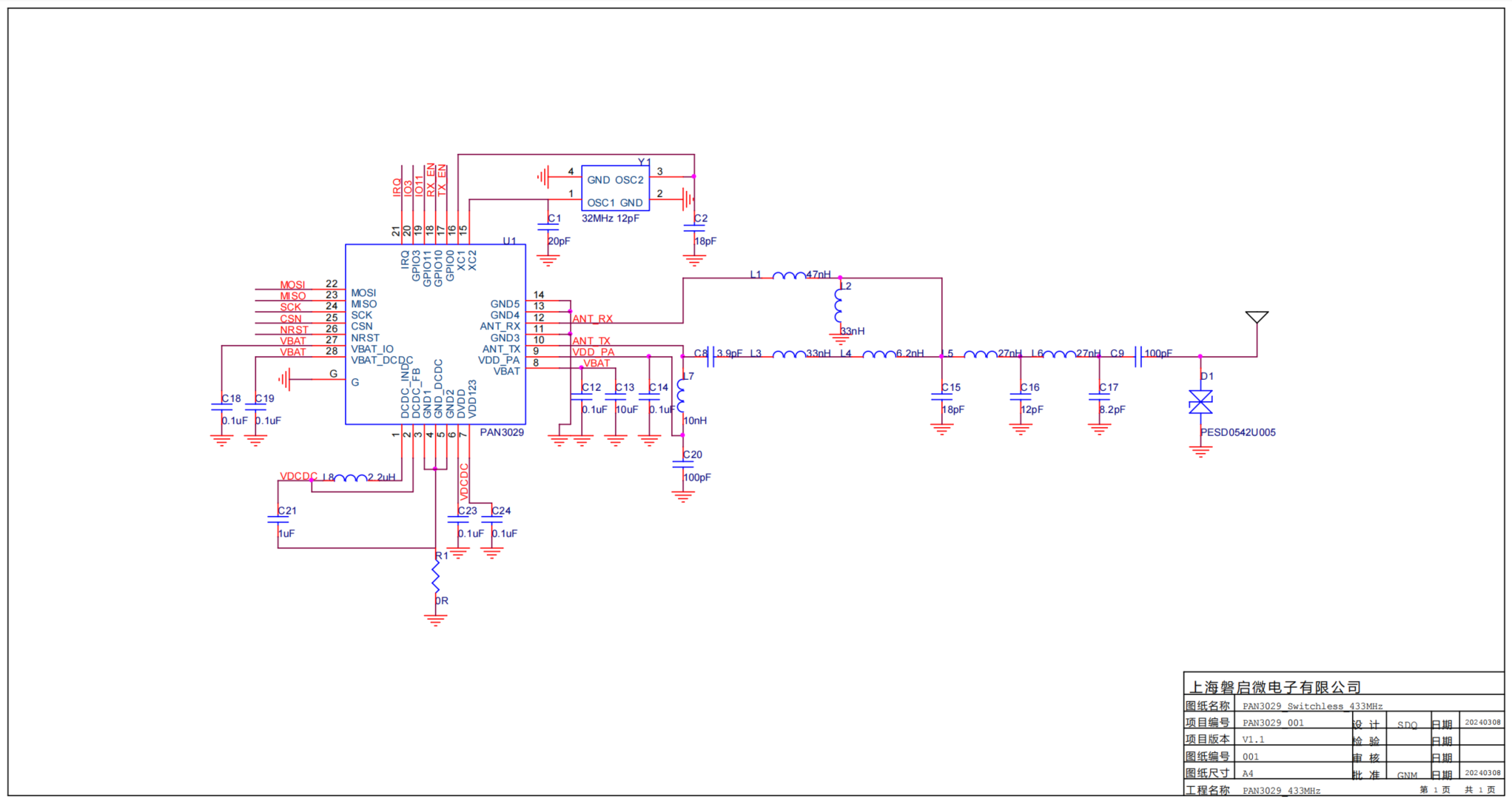

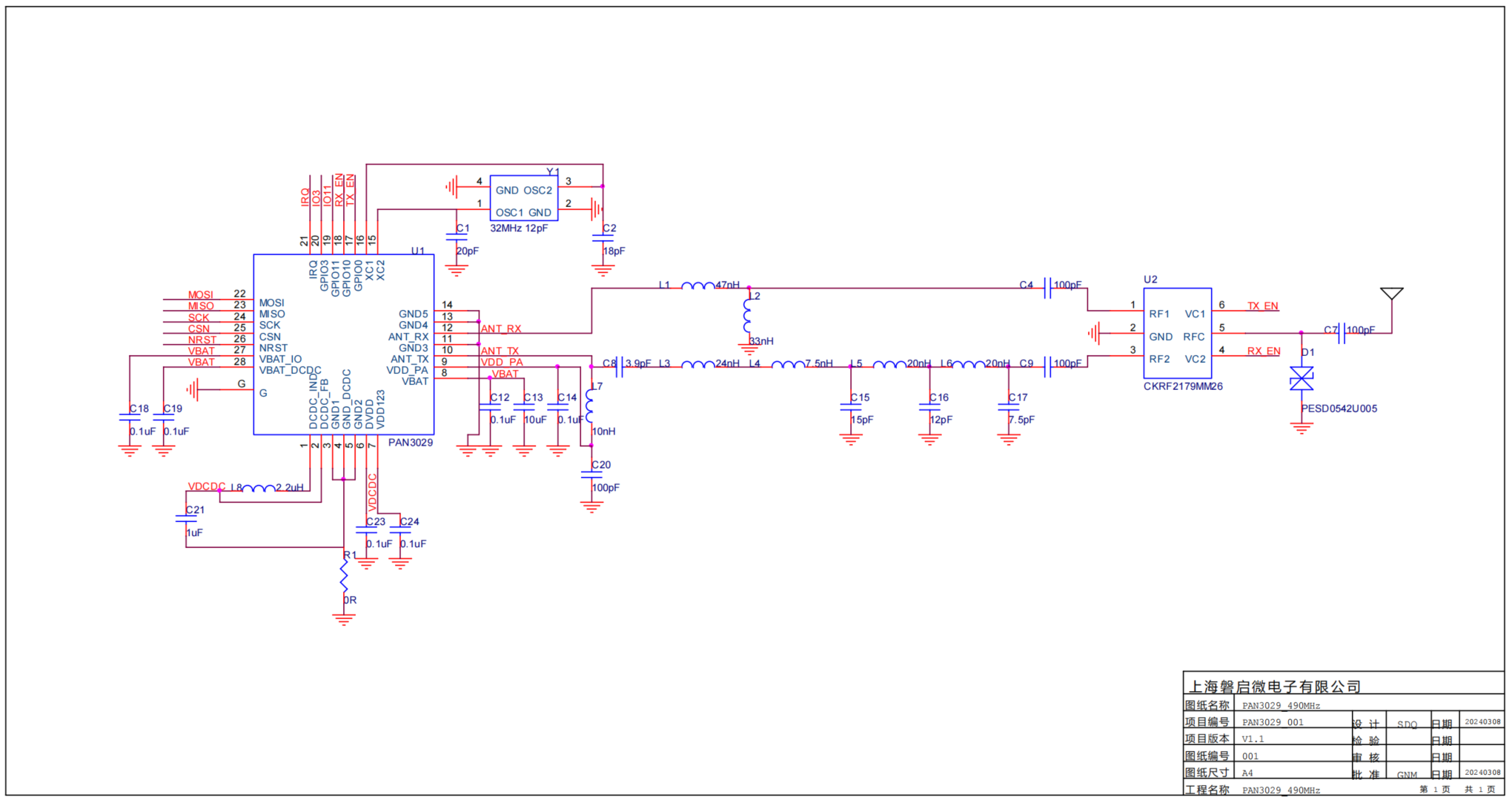

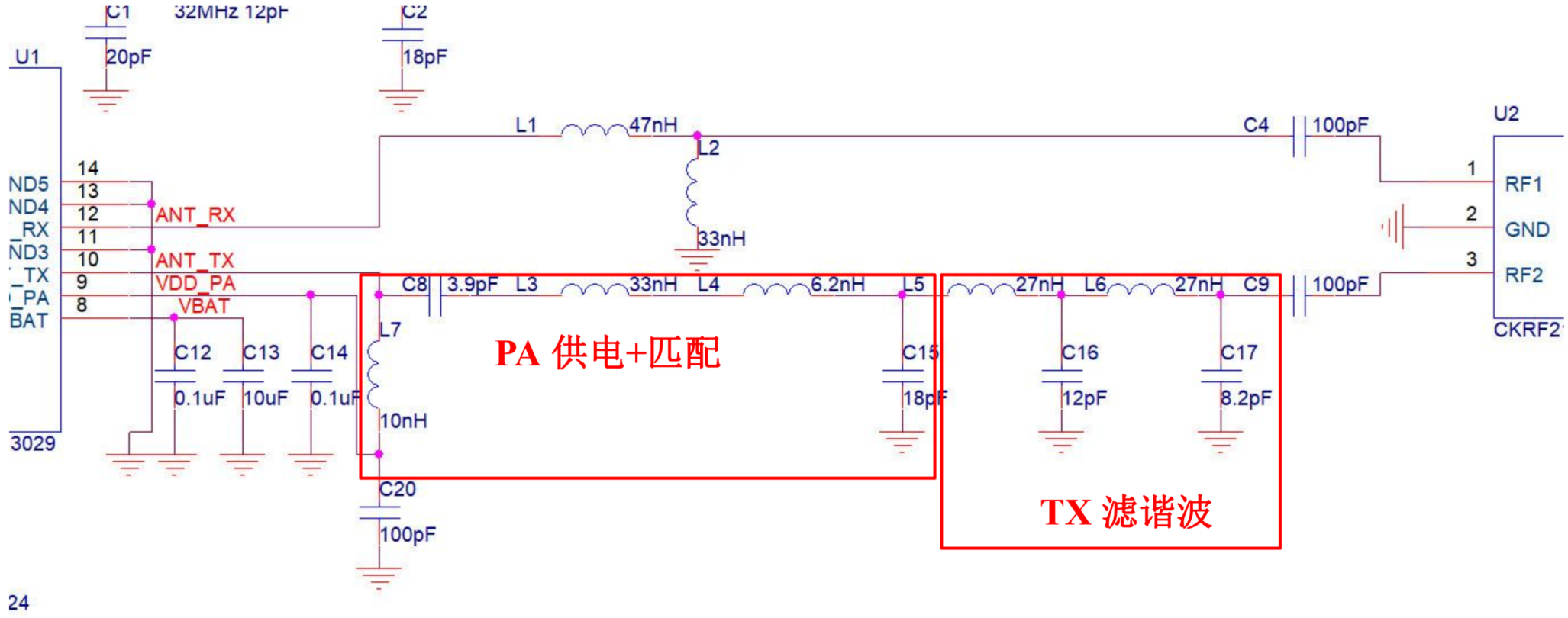

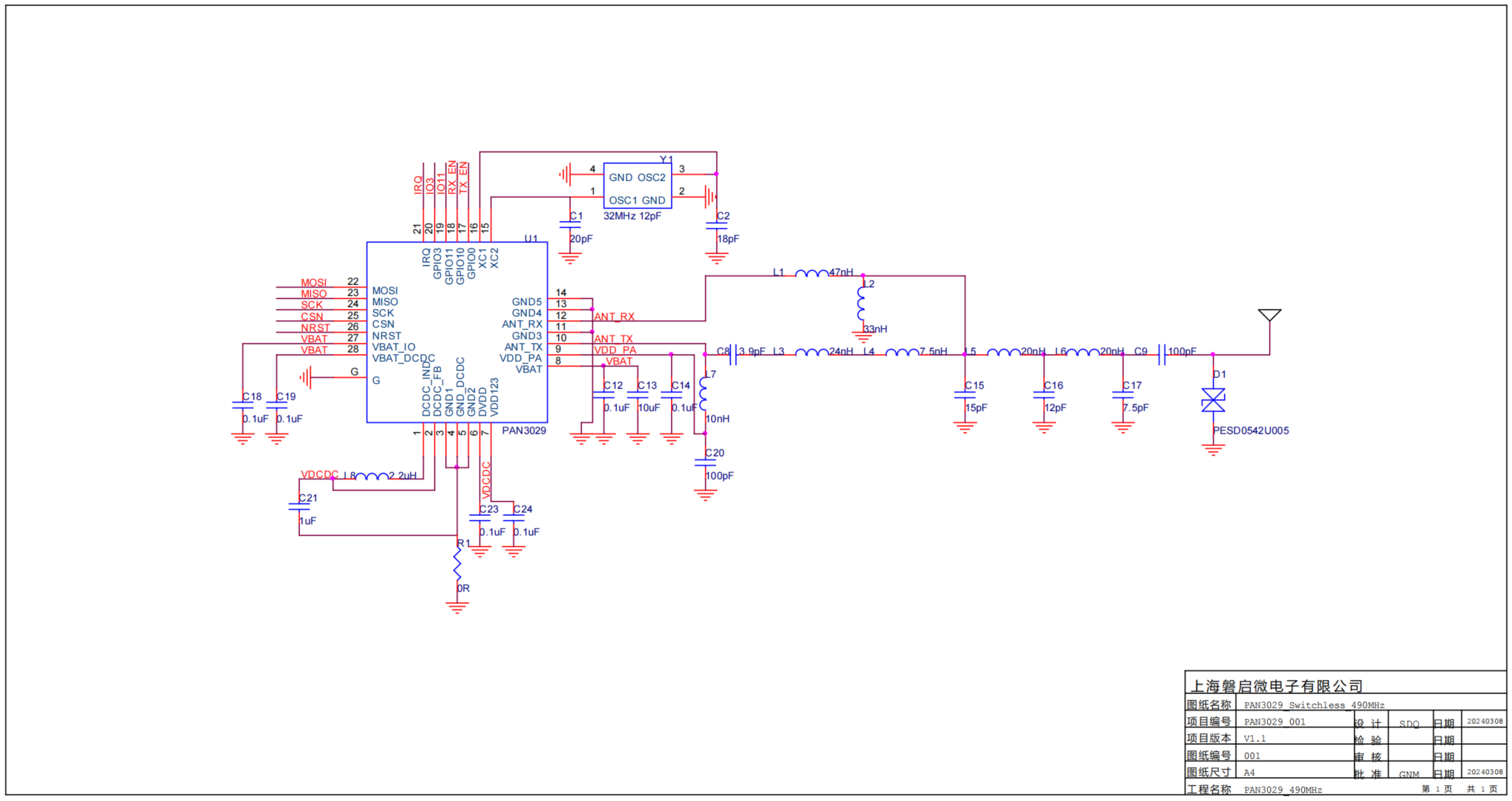

芯片 TX 端电路需要完成给 PA 供电,匹配和滤除谐波功能,PA 供电、匹配和滤谐波分 别对应以下电路。

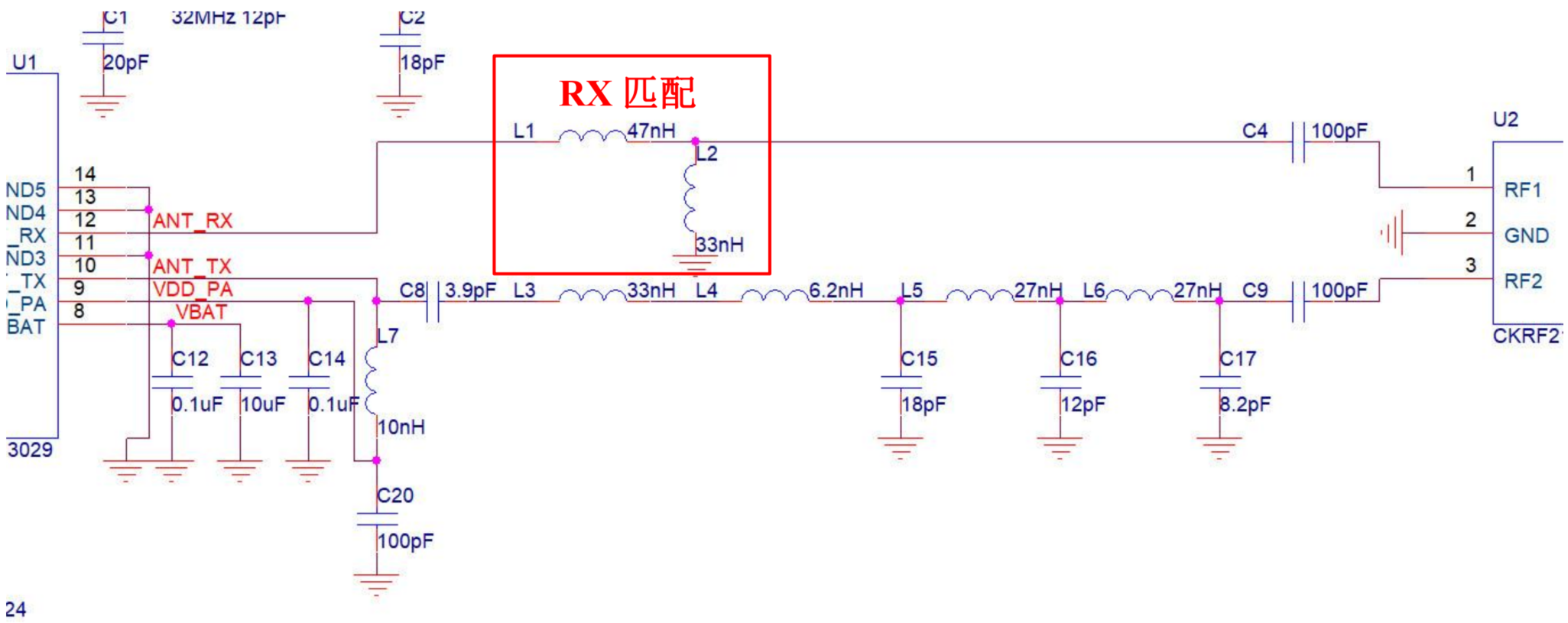

芯片 RX 端电路需要完成匹配功能,对应以下的电路。由于 DCDC 工作后会干扰到 RX ,导 致 RX 灵敏度会有略微的损失,如果对射频性能有很高的要求,建议使用LDO 模式。

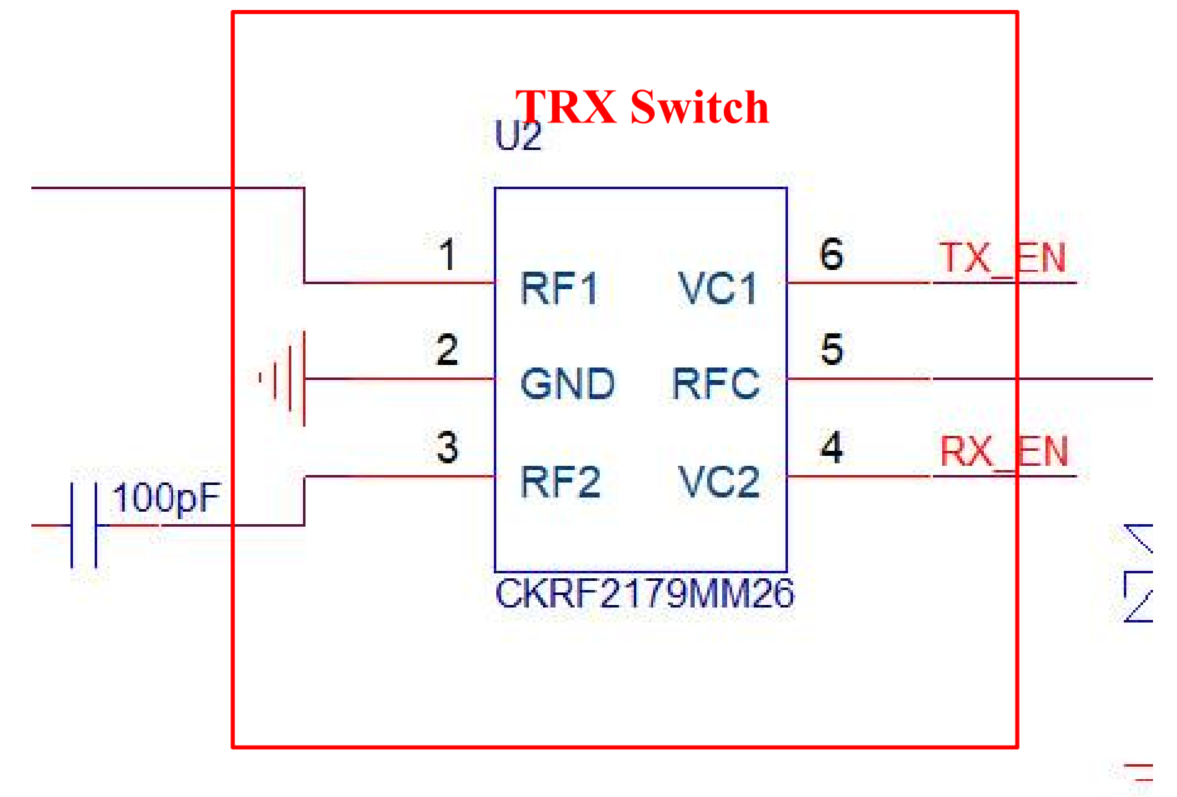

芯片 TX 和 RX 有两种合路方式,一种是通过外部开关合路,这种方式 TX 和 RX 性能能达 到最好的状态;另一种是通过调整电感和电容值直接合路,这种方式 TX 和 RX 性能会受损失, RX 灵敏度在 DCDC 模式下会受到很大的影响。

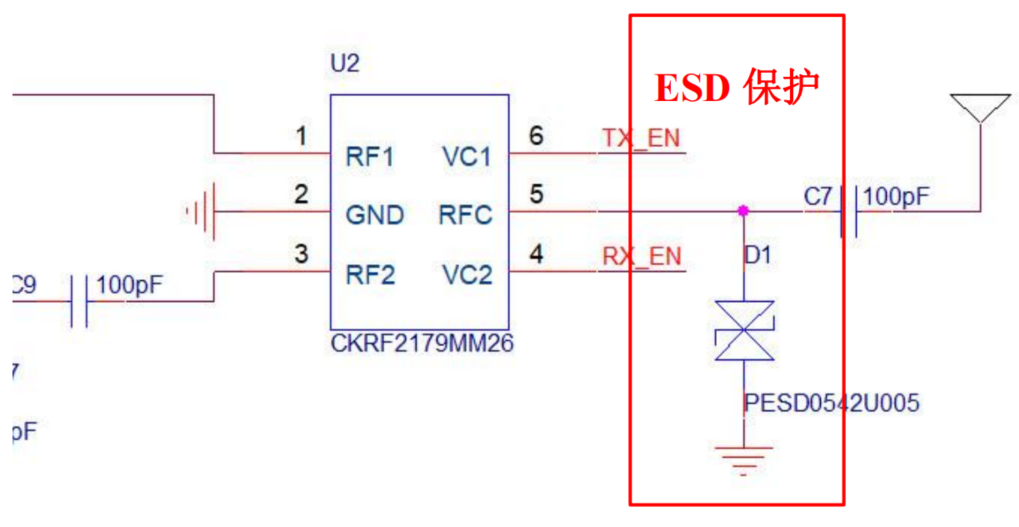

1.6 ESD设计要求¶

天线端 ESD 性能会比其它管脚差一些,需要预留 ESD 保护二极管。

1.7 参考原理图¶

1 、需要将中间的 EPAD 通过顶层的 GND 管脚接到外面的大地上;

2 、DCDC 的地需要通过 0 Ω 电阻与GND 单点连接,不要与GND 地直接相接;

3 、电 感 选 型 要 求 导 通 电 阻 小于 100 m Ω , 峰 值 电 流 大 于 150mA ( 参 考 型 号 : PIM252010-2R2MTS00)。

4 、L5 、C16 、L6 、C17 为安规滤波匹配,如果不考虑安规可以去掉;

5 、匹配元器件值需要根据 TR Switch 和 Layout 的不同微调;

6 、DCDC 模式只推荐在 RX 模式使用,TX 模式 DCDC 打开会影响安规;

1.7.1 433MHz¶

1.7.1.2 参考 BOM¶

位号 |

值 |

描述 |

封装 |

|---|---|---|---|

R1 |

0R |

贴片电阻, ±1% |

0402 |

C8 |

3.9pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C17 |

8.2pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C16 |

12pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C2,C15 |

18pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C1 |

20pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C4,C7,C9,C20 |

100pF |

贴片电容,NPO, ±5% ,50V |

0402 |

C12,C14,C18, |

0.1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C21 |

1uF |

贴片电容,X7R, ±20% ,16V |

0402 |

C13 |

10uF |

贴片电容,X7R, ±20% ,16V |

0603 |

D1 |

- |

PESD0542U005 |

0402 |

L4 |

6.2nH |

LQW15AN6N2G00D |

0402 |

L7 |

10nH |

LQW15AN10NG00D |

0402 |

L5,L6 |

27nH |

LQW15AN27NG00D |

0402 |

L2,L3 |

33nH |

LQW15AN33NG00D |

0402 |

L1 |

47nH |

LQW15AN47NG00D |

0402 |

L8 |

2.2uH |

PIM252010-2R2MTS00 |

2520 |

U1 |

PAN3029 |

- |

QFN28_4*4 |

U2 |

CKRF2179MM26 |

射频开关 |

SOT-363 |

Y1 |

32MHz |

贴片无源晶振,CL=12pF, ±10PPM |

SMD3225 |

1.7.2 433MHz Switchless¶

1.7.2.2 参考BOM¶

位号 |

值 |

描述 |

封装 |

|---|---|---|---|

R1 |

0R |

贴片电阻, ±1% |

0402 |

C8 |

3.9pF |

贴片电容,NPO, ±0.1pF,25V |

0402 |

C17 |

8.2pF |

贴片电容,NPO, ±0.1pF,25V |

0402 |

C16 |

12pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C2,C15 |

18pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C1 |

20pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C9,C20 |

100pF |

贴片电容,NPO, ±5% ,50V |

0402 |

C12,C14,C18, |

0.1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C21 |

1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C13 |

10uF |

贴片电容,X7R, ±20% ,16V |

0603 |

D1 |

- |

PESD0542U005 |

0402 |

L4 |

6.2nH |

LQW15AN6N2G00D |

0402 |

L7 |

10nH |

LQW15AN10NG00D |

0402 |

L5,L6 |

27nH |

LQW15AN27NG00D |

0402 |

L2,L3 |

33nH |

LQW15AN33NG00D |

0402 |

L1 |

47nH |

LQW15AN47NG00D |

0402 |

L8 |

2.2uH |

PIM252010-2R2MTS00 |

2520 |

U1 |

PAN3029 |

- |

QFN28_4*4 |

Y1 |

32MHz |

贴片无源晶振,CL=12pF, ±10PPM |

SMD3225 |

1.7.3 490MHz¶

1.7.3.2 参考BOM¶

位号 |

值 |

描述 |

封装 |

|---|---|---|---|

R1 |

0R |

贴片电阻, ±1% |

0402 |

C8 |

3.9pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C17 |

7.5pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C16 |

12pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C15 |

15pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C2 |

18 pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C1 |

20 pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C4,C7,C9,C20 |

100pF |

贴片电容,NPO, ±5% ,50V |

0402 |

C12,C14,C18, |

0.1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C21 |

1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C13 |

10uF |

贴片电容,X7R, ±20% ,16V |

0603 |

D1 |

- |

PESD0542U005 |

0402 |

L4 |

7.5nH |

LQW15AN7N5G00D |

0402 |

L7 |

10nH |

LQW15AN10NG00D |

0402 |

L5,L6 |

20nH |

LQW15AN20NG00D |

0402 |

L3 |

24nH |

LQW15AN24NG00D |

0402 |

L2 |

33nH |

LQW15AN33NG00D |

0402 |

L1 |

47nH |

LQW15AN47NG00D |

0402 |

L8 |

2.2uH |

PIM252010-2R2MTS00 |

2520 |

U1 |

PAN3029 |

- |

QFN28_4*4 |

U2 |

CKRF2179MM26 |

射频开关 |

SOT-363 |

Y1 |

32MHz |

贴片无源晶振,CL=12pF, ±10PPM |

SMD3225 |

1.7.4 490MHz Switchless¶

1.7.4.1 参考原理图¶

1.7.4.2 参考BOM

位号 |

值 |

描述 |

封装 |

|---|---|---|---|

R1 |

0R |

贴片电阻, ±1% |

0402 |

C8 |

3.9pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C17 |

7.5pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C16 |

12pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C15 |

15pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C2 |

18 pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C1 |

20 pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C9,C20 |

100pF |

贴片电容,NPO, ±5% ,50V |

0402 |

C12,C14,C18,C19,C23,C24 |

0.1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C21 |

1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C13 |

10uF |

贴片电容,X7R, ±20% ,16V |

0603 |

D1 |

- |

PESD0542U005 |

0402 |

L4 |

7.5nH |

LQW15AN7N5G00D |

0402 |

L7 |

10nH |

LQW15AN10NG00D |

0402 |

L5,L6 |

20nH |

LQW15AN20NG00D |

0402 |

L3 |

24nH |

LQW15AN24NG00D |

0402 |

L2 |

33nH |

LQW15AN33NG00D |

0402 |

L1 |

47nH |

LQW15AN47NG00D |

0402 |

L8 |

2.2uH |

PIM252010-2R2MTS00 |

2520 |

U1 |

PAN3029 |

- |

QFN28_4*4 |

Y1 |

32MHz |

贴片无源晶振,CL=12pF, ±10PPM |

SMD3225 |

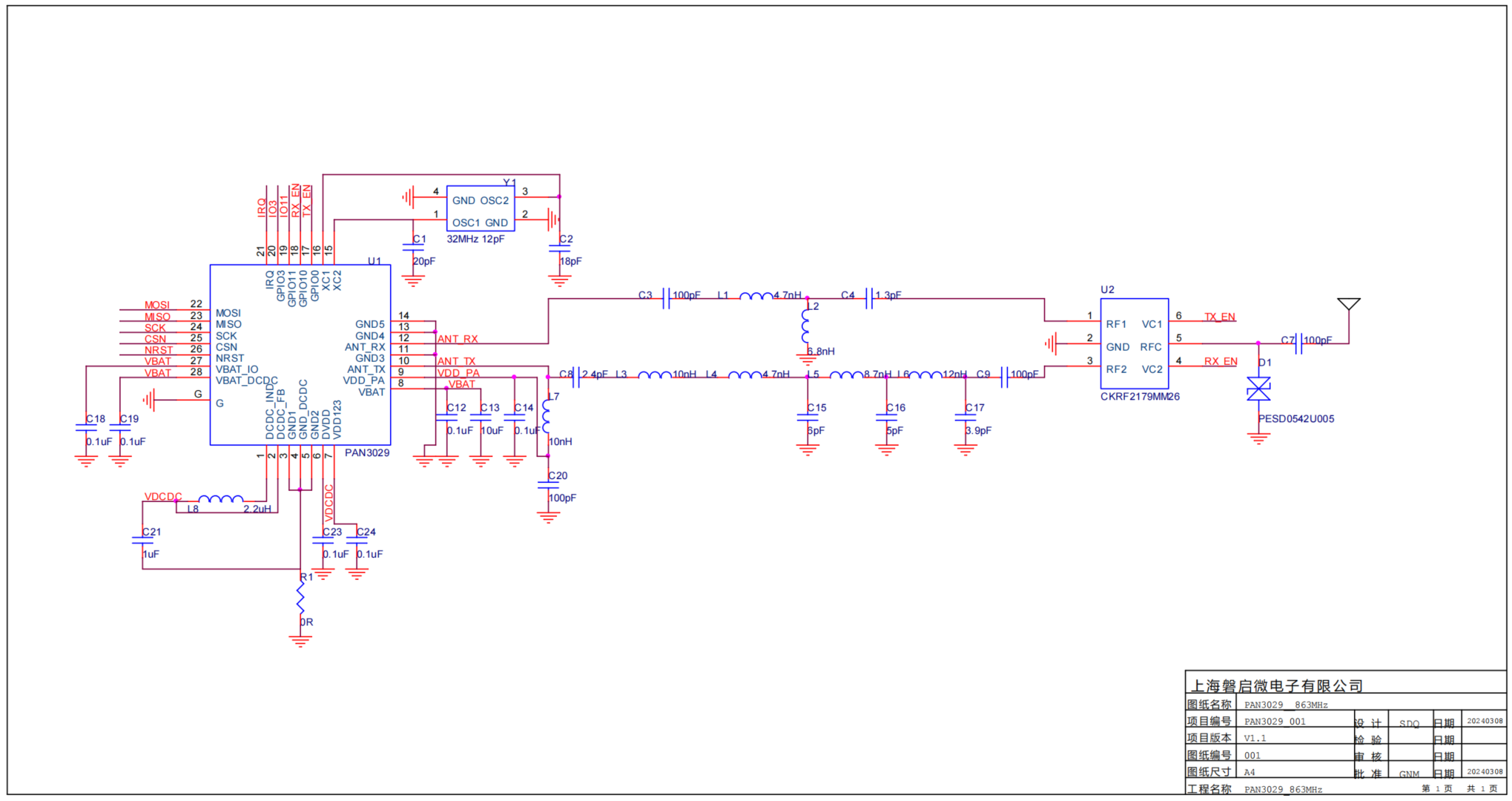

1.7.5 863MHz¶

1.7.5.2 参考BOM¶

位号 |

值 |

描述 |

封装 |

|---|---|---|---|

C4 |

1.3pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C8 |

2.4pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C17 |

3.9pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C16 |

5pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C15 |

6pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C2 |

18pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C1 |

20pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C3,C7,C9,C20 |

100pF |

贴片电容,NPO, ±5% ,50V |

0402 |

C12,C14,C18,C19,C23,C24 |

0.1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C21 |

1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C13 |

10uF |

贴片电容,X7R, ±20% ,16V |

0603 |

D1 |

- |

PESD0542U005 |

0402 |

L1,L4 |

4.7nH |

LQW15AN4N7G00D |

0402 |

L2 |

6.8 nH |

LQW15AN6N8G00D |

0402 |

L5 |

8.7nH |

LQW15AN8N7G00D |

0402 |

L3,L7 |

10nH |

LQW15AN10NG00D |

0402 |

L6 |

12nH |

LQW15AN12NG00D |

0402 |

L8 |

2.2uH |

PIM252010-2R2MTS00 |

2520 |

U1 |

PAN3029 |

- |

QFN28_4*4 |

U2 |

CKRF2179MM26 |

射频开关 |

SOT-363 |

Y1 |

32MHz |

贴片无源晶振,CL=12pF, ±10PPM |

SMD3225 |

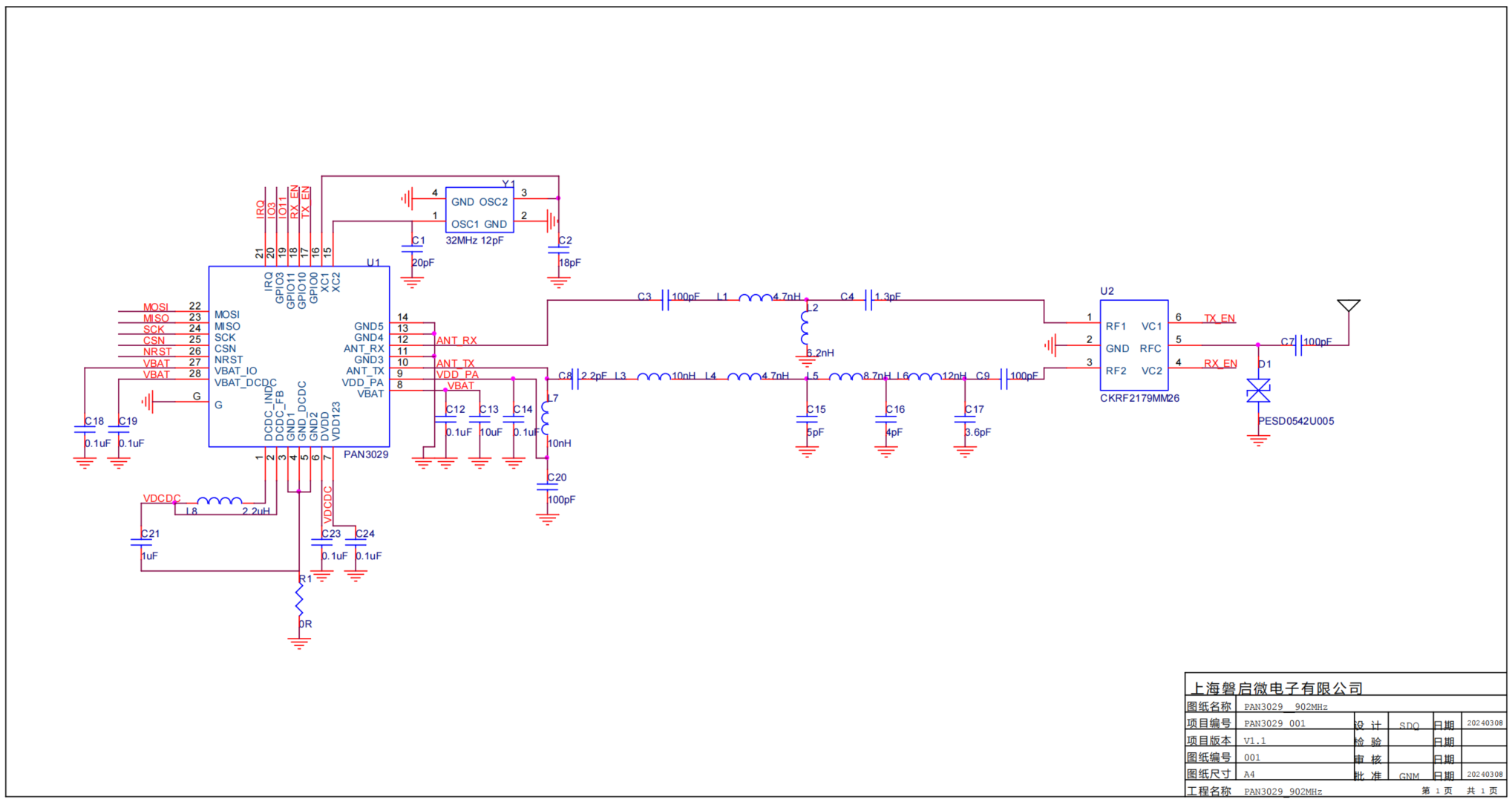

1.7.6 915MHz¶

1.7.6.2参考BOM¶

位号 |

值 |

描述 |

封装 |

|---|---|---|---|

C4 |

1.3pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C8 |

2.2pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C17 |

3.6pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C16 |

4pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C15 |

5pF |

贴片电容,NPO, ±0.1pF,50V |

0402 |

C2 |

18pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C1 |

20pF |

贴片电容,NPO, ±1% ,50V |

0402 |

C3,C7,C9,C20 |

100pF |

贴片电容,NPO, ±5% ,50V |

0402 |

C12,C14,C18,C19,C23,C24 |

0.1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C21 |

1uF |

贴片电容,X7R, ±10% ,16V |

0402 |

C13 |

10uF |

贴片电容,X7R, ±20% ,16V |

0603 |

D1 |

- |

PESD0542U005 |

0402 |

L1,L4 |

4.7nH |

LQW15AN4N7G00D |

0402 |

L2 |

6.2nH |

LQW15AN6N2G00D |

0402 |

L5 |

8.7nH |

LQW15AN8N7G00D |

0402 |

L3,L7 |

10nH |

LQW15AN10NG00D |

0402 |

L6 |

12nH |

LQW15AN12NG00D |

0402 |

L8 |

2.2uH |

PIM252010-2R2MTS00 |

2520 |

U1 |

PAN3029 |

- |

QFN28_4*4 |

U2 |

CKRF2179MM26 |

射频开关 |

SOT-363 |

Y1 |

32MHz |

贴片无源晶振,CL=12pF, ±10PPM |

SMD3225 |

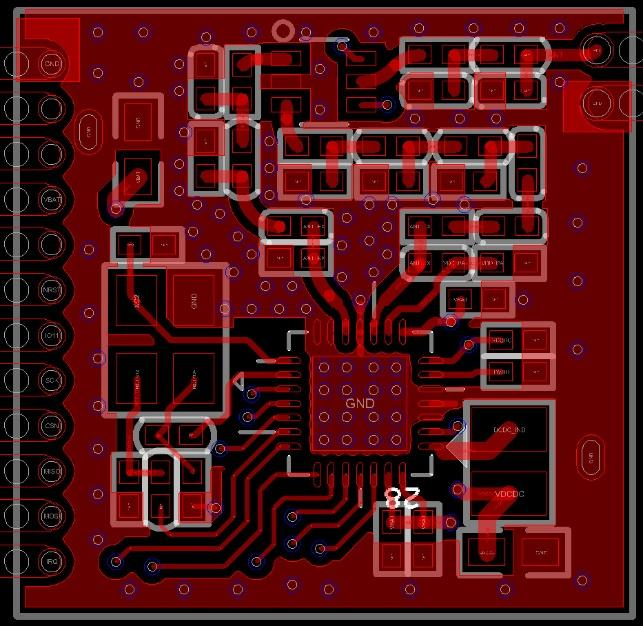

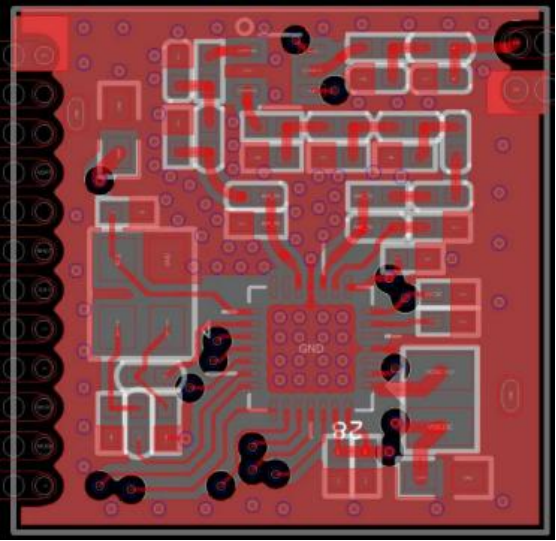

2. PCB设计要求¶

2.1 板材的选择和特殊说明¶

关于 PCB 设计,建议使用四层板,四层板安规特性更好,如需考虑成本等因素,使用两层

板布局,需要将中间的 EPAD 通过顶层 GND 脚接到外面的大地上,同时中间的 EPAD 接地过孔

尽可能多,比如 16 个。

2.3 电源和地线LAYOUT¶

电源线宽度要求能达到 0.5mm 以上,承受 200 毫安的瞬态电流。在靠近芯片电源引脚放置 去耦电容,其中小容值电容摆放在更靠近芯片引脚的位置,以便较好地滤除高频噪声。

建议电源线和地线采用放射状的连接方式,单点接电源/地并且单独走线,RF 芯片的电源/ 地线走线与其它芯片或器件分开来,从总参考电源/地线单独引线,防止受到干扰。如果是从 LDO 或者 DCDC 等器件引出电源线,也需要单独引线并且做好滤波措施。芯片底部的 GND 引脚需要 和电路板顶层的GND 平面直接相连。

另外,覆地的地线也建议与噪声较少的地线或者总参考地线连接,不与强信号或者强干扰器 件地线电源线相连,可以有效地减少整个印制板的工作噪声。

2.4 晶振相关的LAYOUT¶

1 、在面积允许的程度下,晶体跟芯片之间保持一定的距离,做好隔热处理

2 、直插的晶振的焊盘需要保证外径与内径差值有 0.2mm 以上;

3 、为防止晶振信号干扰到射频信号,印制板上在晶振焊盘和走线的两边需要做覆地处理;

4 、为避免晶振受到天线的发射功率干扰,印制板上的天线部分与晶振焊盘走线部分之间要 用 0.5mm 以上地线作为间隔带,同时晶振的外壳需要离天线 3mm 以上。

2.5 控制线LAYOUT¶

控制类的 SPI 线、IRQ 线需要减少走线干扰,布线时走线较短并且走线两边有完整的覆地。

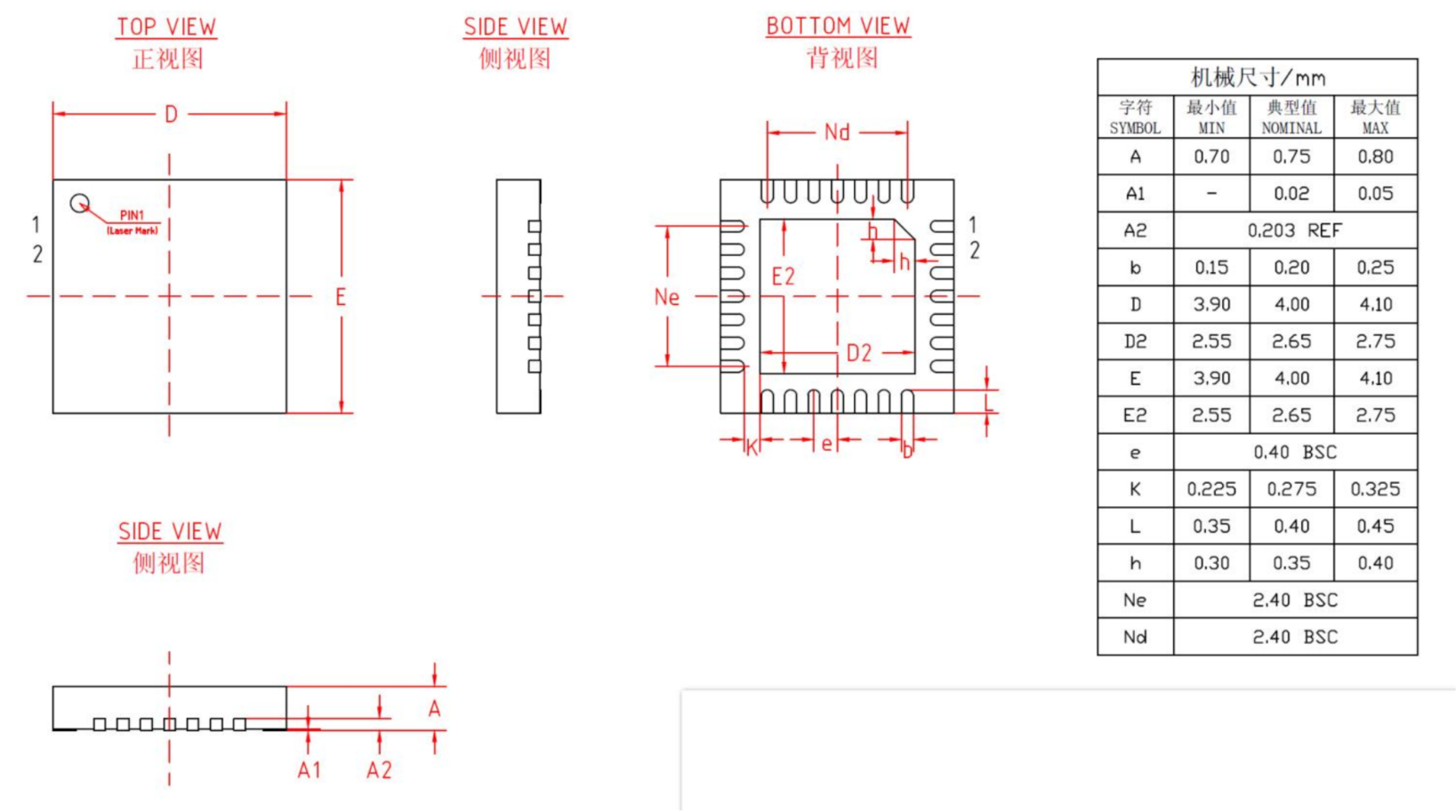

2.6 QFN封装LAYOUT¶

PAN3029(4mm×4mm 的 QFN 封装的芯片) ,其芯片底下焊盘需要接地;PCB 做库元件时, 在芯片中心需加接地的大 Pad ,为保证与双层 PCB 的 Bottom层的地平面较好连接,Pad 中心建 议用 16 个过孔,同时中间的 EPAD 通过顶层的 NC 脚接到外面的大地上。

PAN3029 芯片下面的 PCB 板的 Bottom层尽量不要有走线和元器件,特别是靠近射频匹配电 路的部分,完整的地平面能保证良好的射频性能。

2.7 射频匹配电路LAYOUT¶

射频匹配部分结构要严格按照原理图推荐值来设计,由于布局差异可微调元器件值。射频匹

配元器件 layout 原则:

1 、为了防止射频前端能量损耗,从管脚 ANT 到天线的走线较短,并且按照50 欧姆阻抗走 线(与周边铺地间距 0.3mm,背面完整的参考地),射频匹配部分走线周边的铺地要连贯牢固(多 打过孔),可以使得发射能量较多地从天线端出去;

2 、为了保证阻抗的连续性,射频匹配部分对应的背面参考地要避免放置元器件和走线,需 要完整的地平面;

3 、覆地建议用实心地;

4 、天线旁边的GND 可以预留露铜,方便焊接调试天线;

5 、RF 参考地和 EPAD 需要良好连接;

6 、禁止射频线打过孔换层。

3. 特殊注意点¶

3.1 PA输出功率¶

需要严格按照 SDK 推荐的档位来配置,否则会引入其它风险,影响应用。

3.2 DCDC模式接收¶

引脚 3 、4 和 5 需要通过 0 Ω 电阻和GND 单点连接,否则 DCDC 打开会影响接收灵敏度。

3.4 Layout特殊要求¶

关于 PCB 设计,建议使用四层板,四层板安规特性更好,如需考虑成本等因素,使用两层

板布局,需要将中间的 EPAD 通过顶层的 GND 脚接到外面的大地上,同时中间的 EPAD 接地过

孔尽可能多,比如 16 个,示意图如下图所示,否则会出现大功率不锁定的异常。863MHz 和

915MHz 输出功率超过 14dBm 时需要四层板布局,否则会出现不锁定的异常。