PAN108x 硬件参考设计¶

1 概述¶

本文档主要介绍 PAN1080Ux1x/PAN1083Ux1x/PAN108xUx3x/PAN108xLx5x芯片方案的硬件原理图设计、PCB 设计建议、天线设计、静电防护、RF性能等,以及提供一些外围电路的硬件设计方法。

2 原理图设计¶

2.1 PAN108x参考设计原理图¶

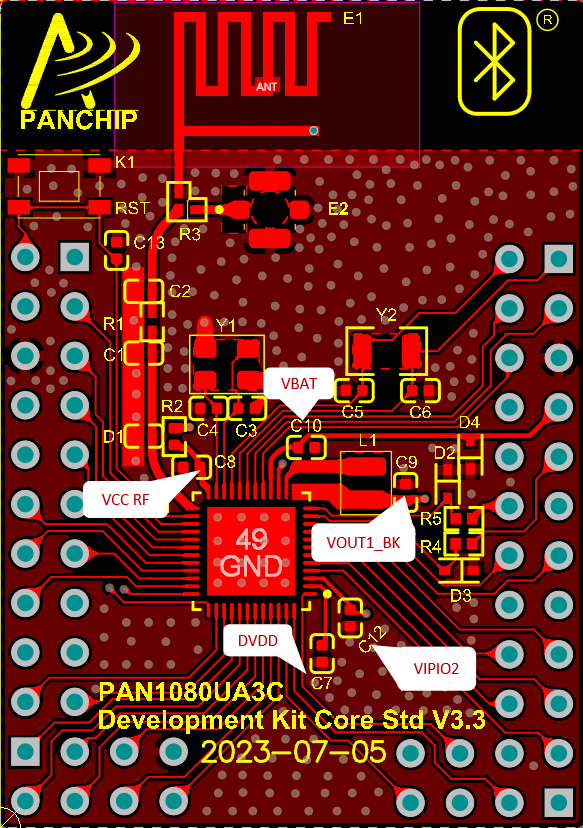

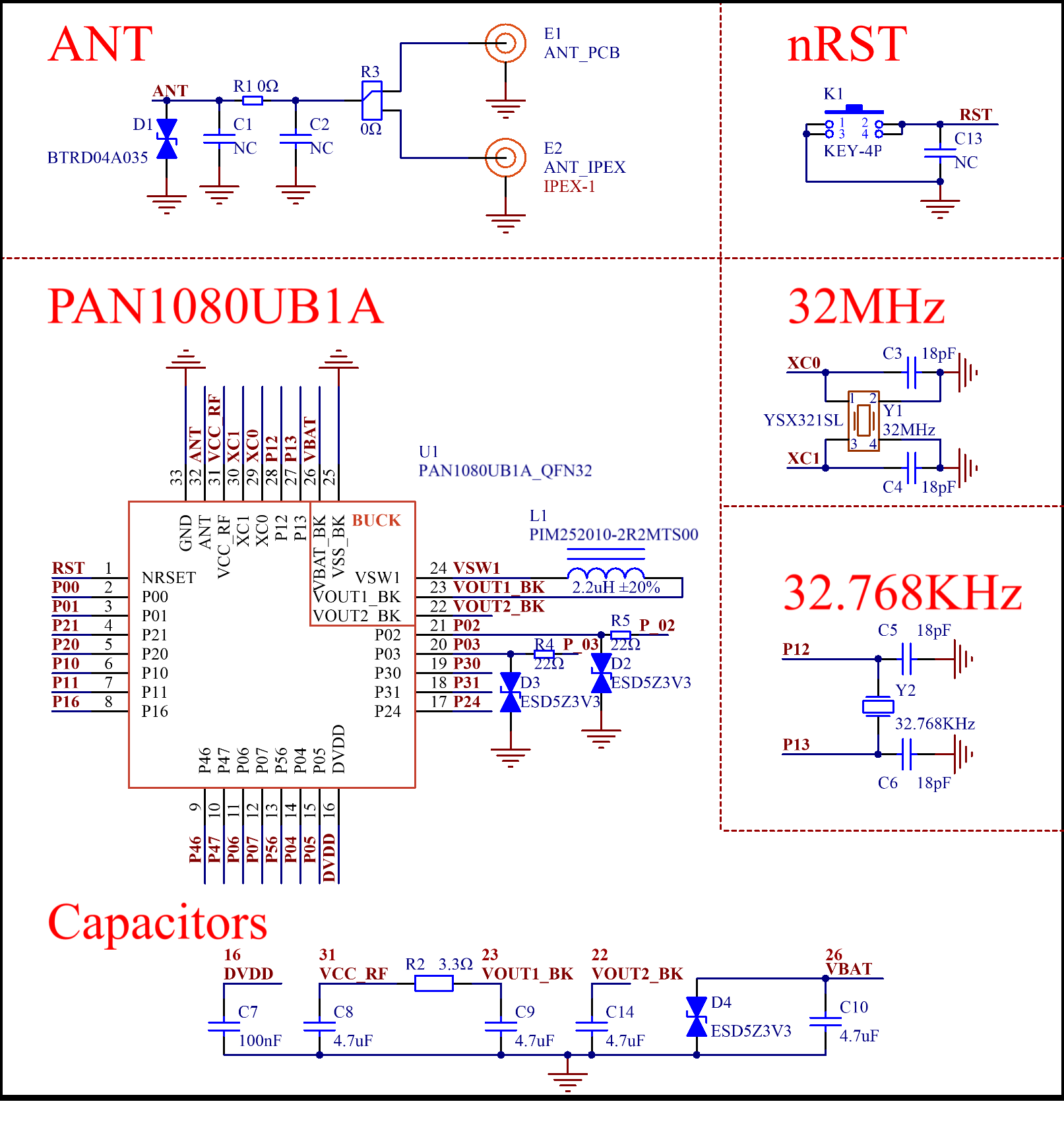

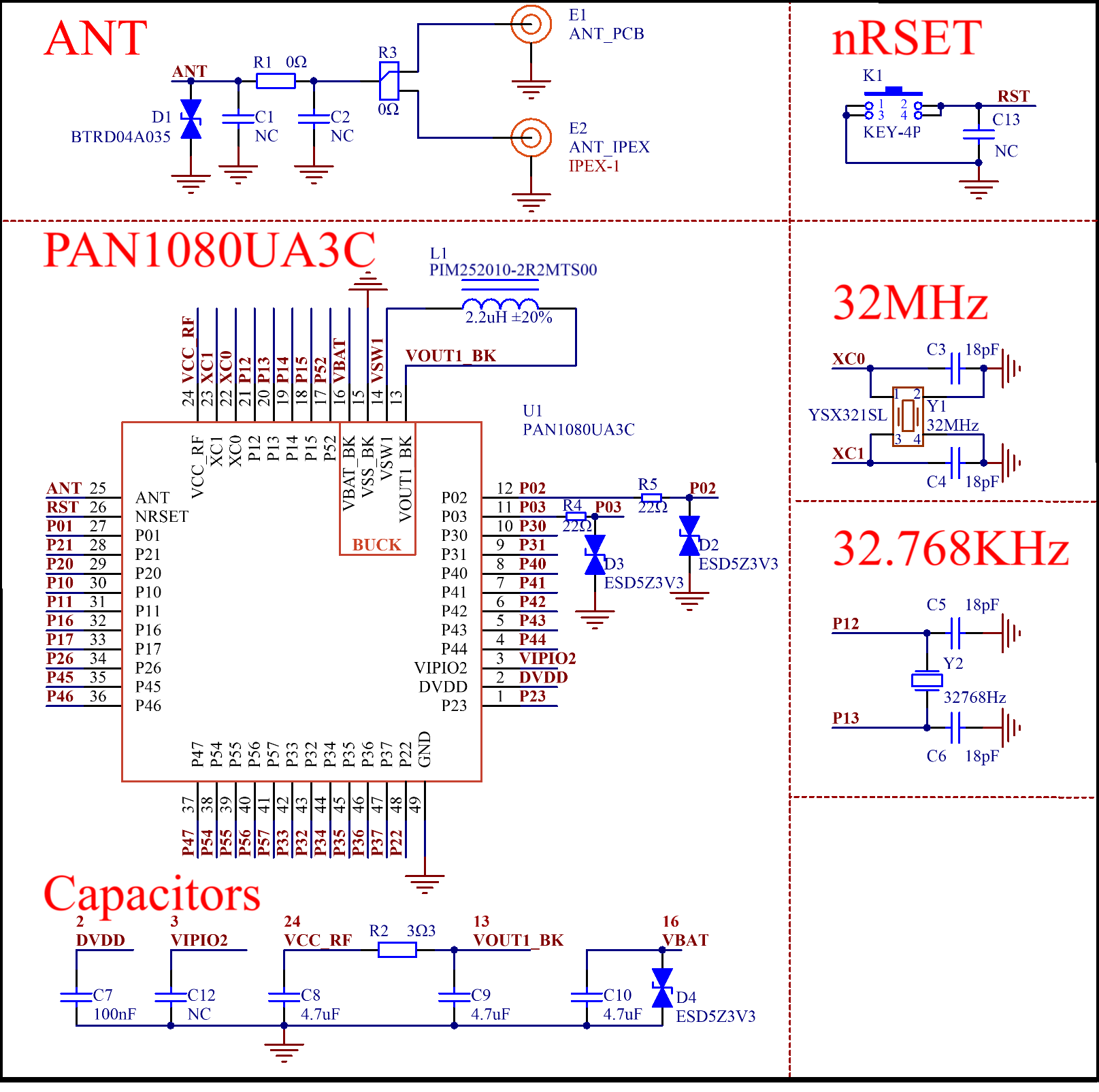

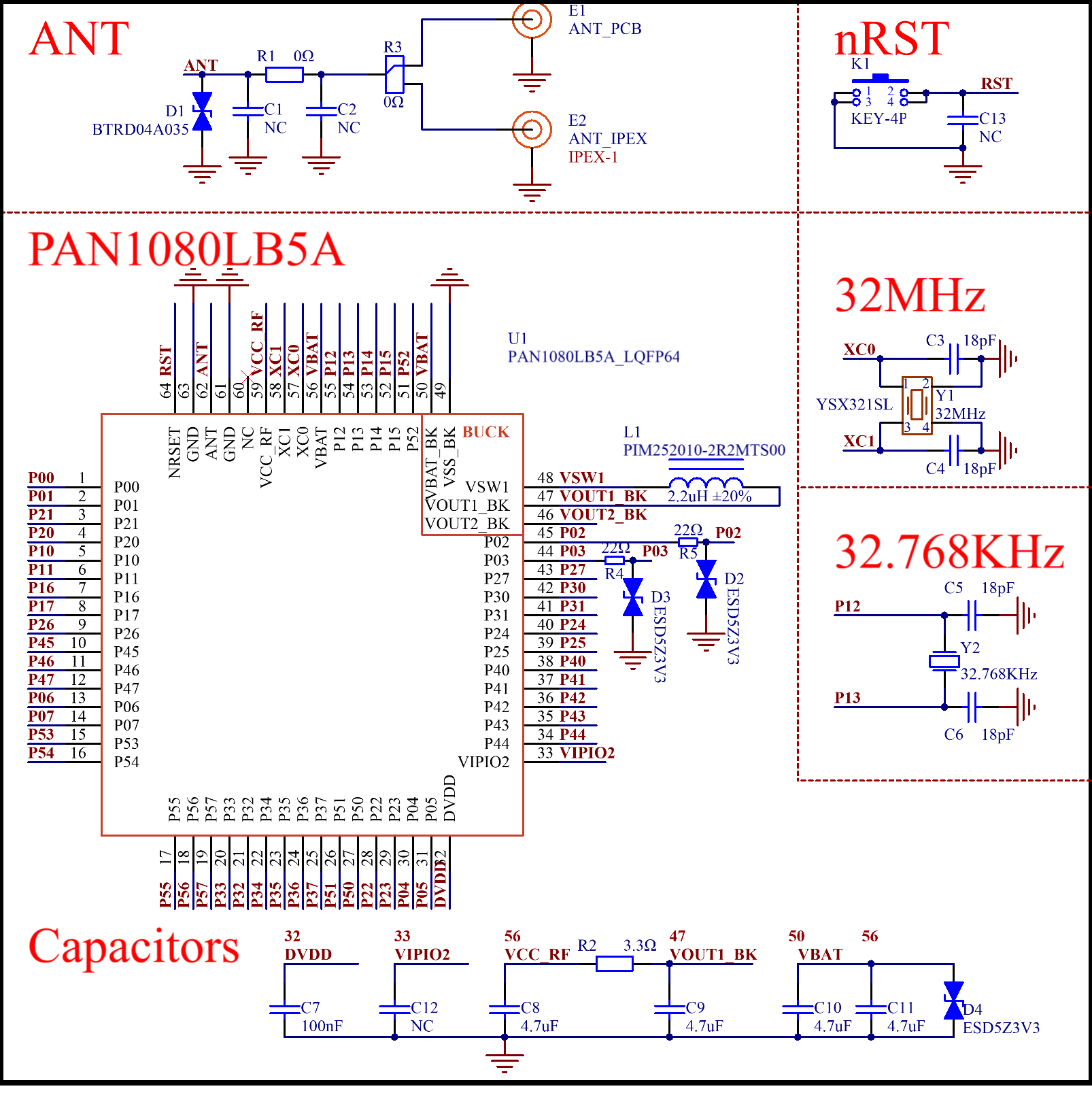

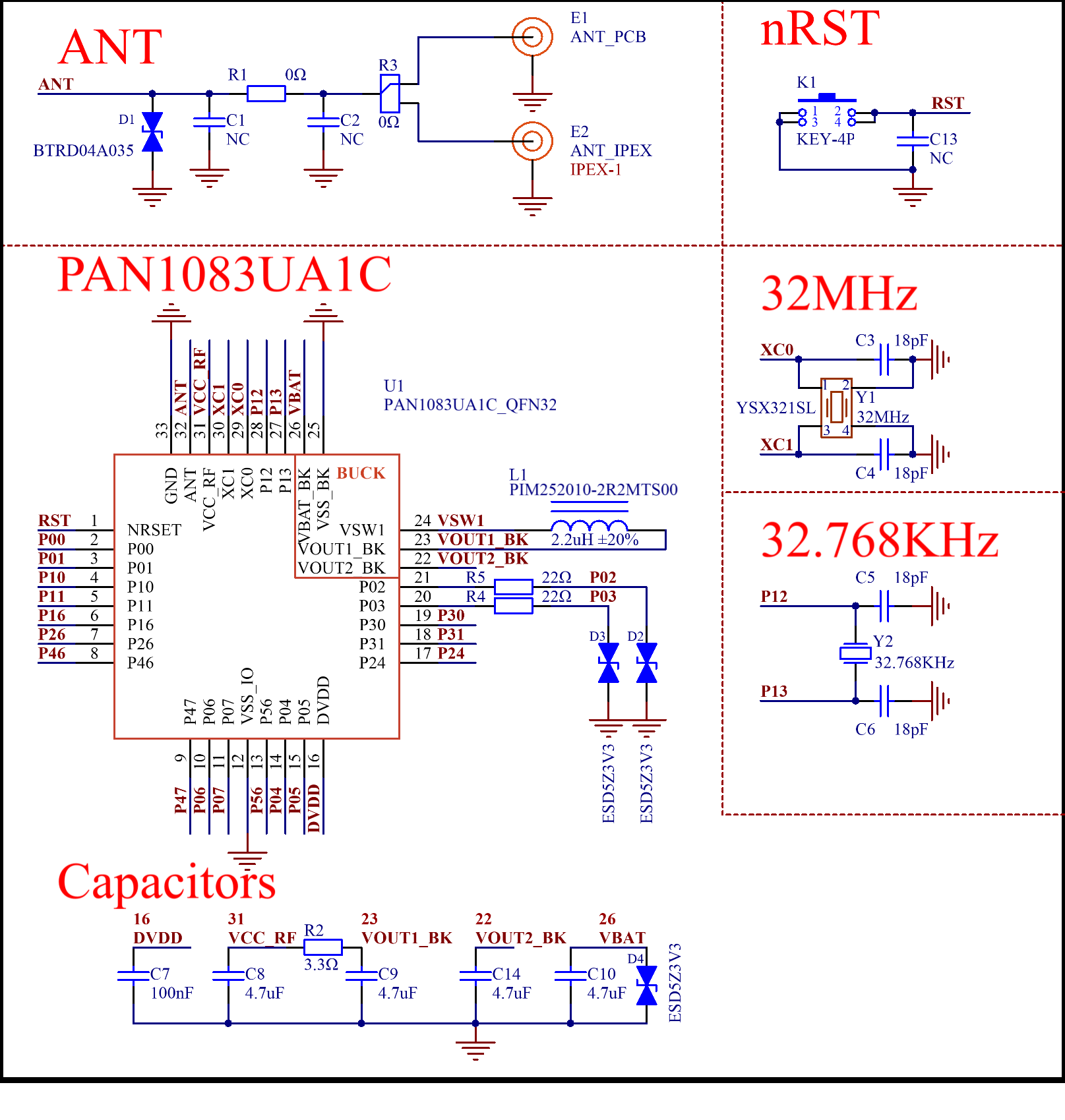

如下图,电路系统由DC-DC降压、晶振电路、天线匹配网络和一些电容组成。

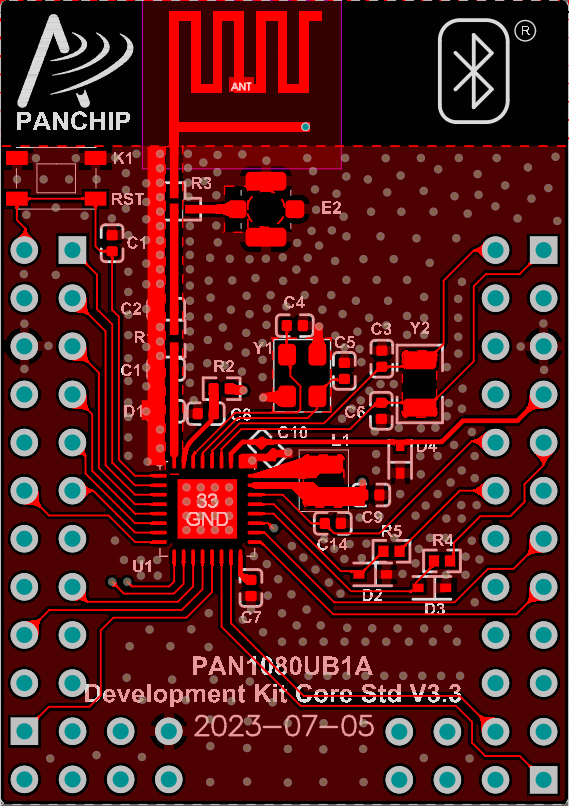

PAN108xUx1x最小系统参考设计原理图¶

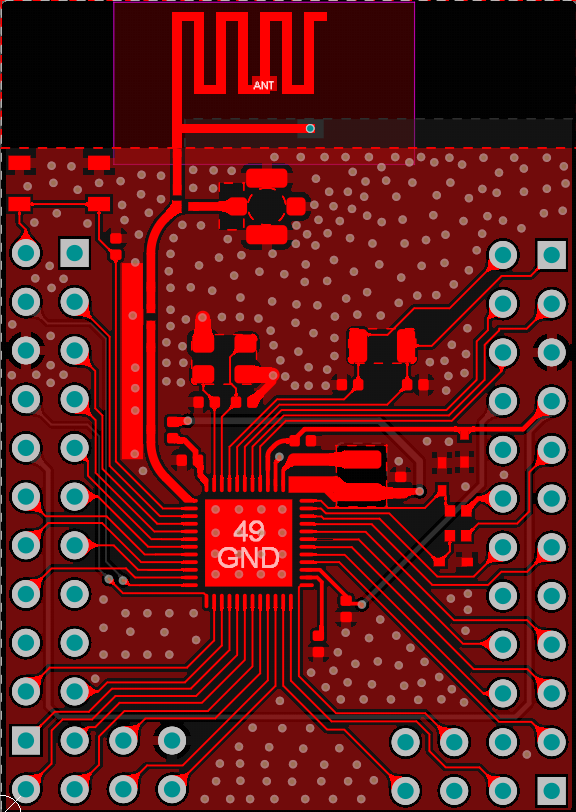

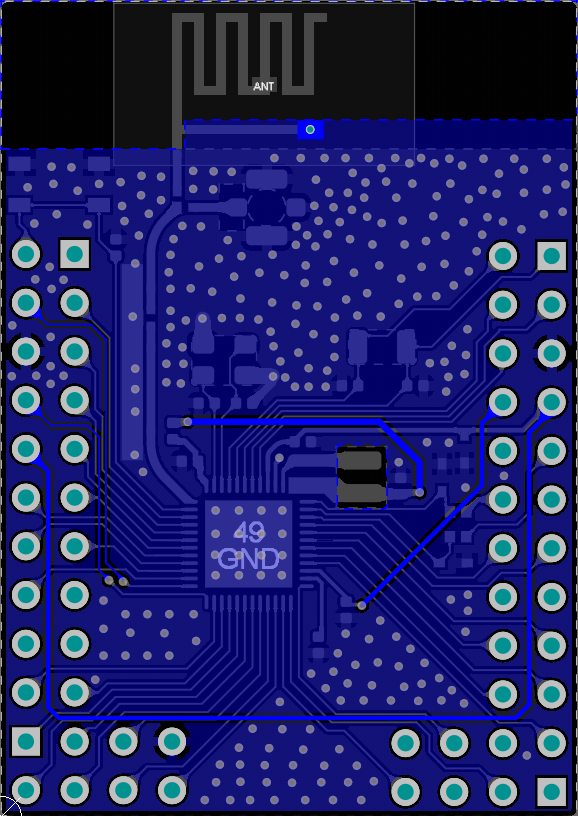

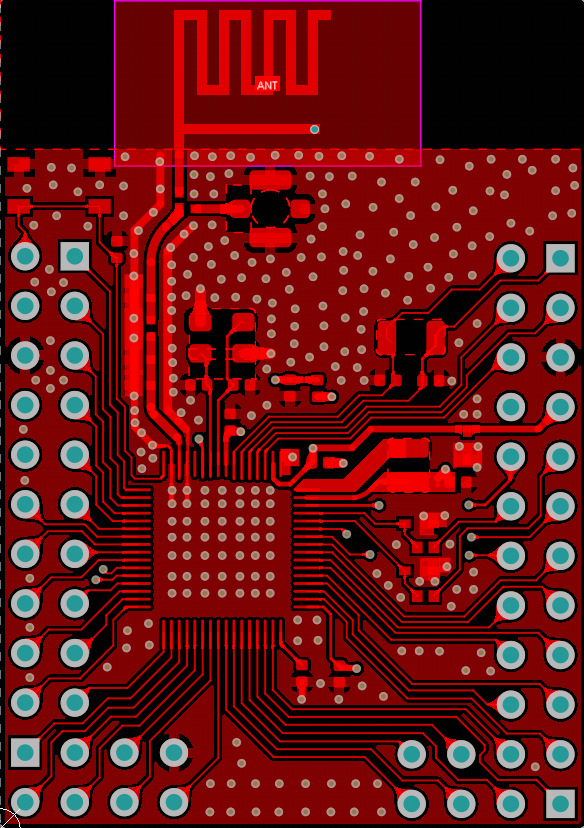

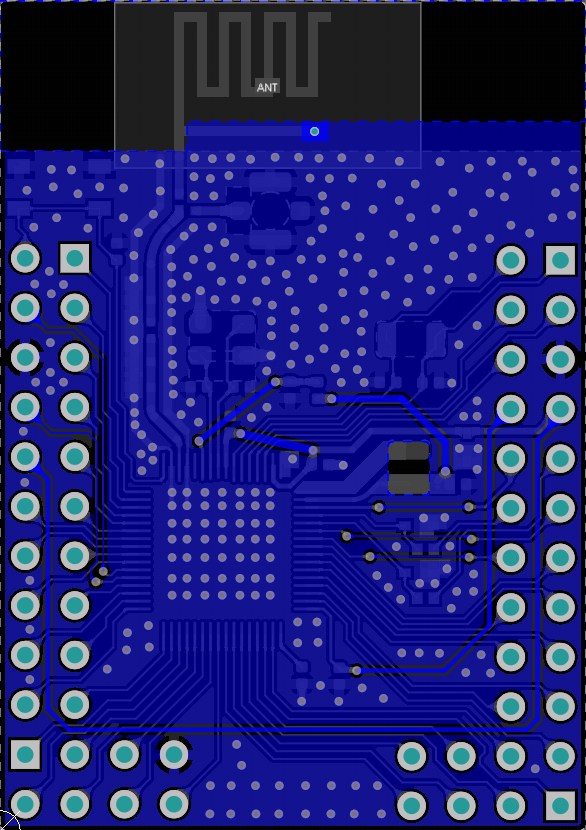

PAN108xUx3x最小系统参考设计原理图¶

PAN108xLx5x最小系统参考设计原理图¶

PAN1083Ux1x最小系统参考设计原理图¶

2.2 电源¶

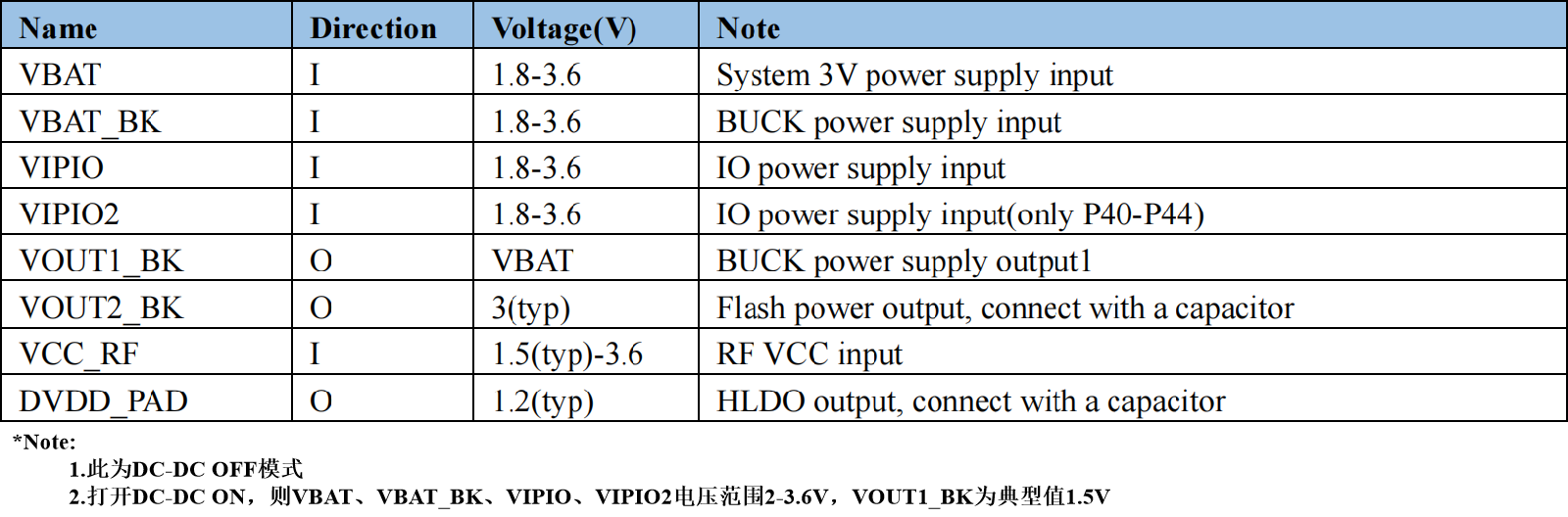

VBAT为芯片电源脚,要求供电能力不小于60mA,供电范围为1.8V–3.6V*;

DVDD、VCC_RF、VBAT(PAN108xLx5x芯片有VBAT和VBAT_BK)、VOUT1_BK 至少预留1个电容(32PIN封装的芯片,VOUT2_BK需要预留1个电容),预留一大一小2个电容更佳,应尽可能靠近芯片引脚摆放;

VIPIO2 外部电容可以省略,详见章节2.2.4;

*注:DC-DC OFF(DC-DC ON模式下工作电压范围2V–3.6V)

电源电压范围表¶

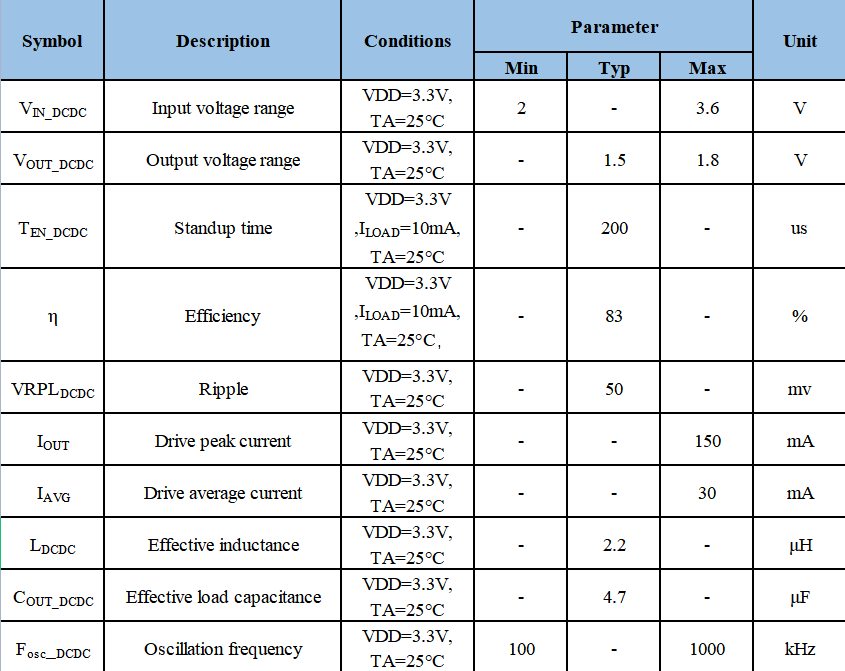

2.2.1 DC-DC¶

DC-DC 外围电路

外围电路组成为:L1、C9;

要求L1指定型号: PIM252010-2R2MTS00,参数详见章节5——BOM。

DC-DC的两种工作模式:

开启DC-DC模式可以降低系统功耗;

开启LDO(Bypass)模式后芯片内部将VBAT连接到VSW1,这时VSW1处的2.2uH电感作用为一段导体,可以用0Ω电阻替换;

DC-DC、LDO两种模式不能同时开启;

在不考虑功耗的前提下,可将VCC_RF直接连接到VBAT,此时应将电源模式设置为LDO模式。

DC-DC相关引脚说明:

VBAT_BK为DC-DC的供电引脚,在QFN封装中VBAT_BK与VBAT共同使用同一引脚;

VSW1为DC-DC的功率开关(P-MOS)漏极输出引脚,功率电感应靠近该引脚放置;

VOUT1_BK为DC-DC的反馈引脚,电容应靠近该引脚放置;

VOUT2_BK为内部Flash供电,其供电电压为3V*;

VSS_BK为DC-DC电源的GND引脚。

*注:3V为典型值

DC-DC基本特性表¶

2.2.3 VCC_RF¶

VCC_RF外部需要接一级RC滤波器并尽量靠近该引脚。R2为3.3Ω、C8为4.7uF,截止频率约为:10KHz。

2.2.4 VIPIO2¶

VIPIO2电源脚在QFN48、LQFP64 封装上有独立的PIN脚。 因此PAN108xUx3x、PAN108xLx5x 可配置两组不同的IO输出电平。P40、P41、P42、P43、P44输出的高电平为VIPIO2的电压。 其余IO输出的高电平为VBAT电压。VIPIO2输入电压范围为1.8V–VBAT。

VIPIO2电源脚在QFN32 封装上和VBAT脚绑定在一起。因此PAN108xUx1x GPIO输出的高电平为VBAT电压。

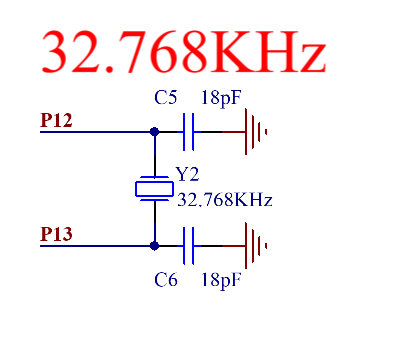

2.3 晶振¶

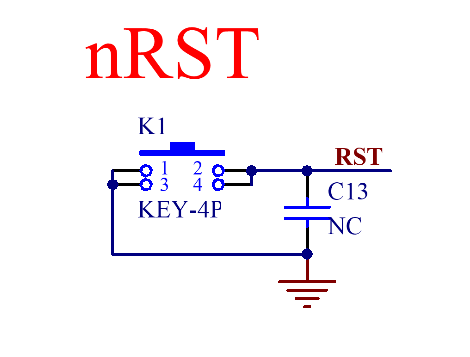

2.4 复位电路¶

复位引脚可以悬空,或增加外部按键。在外部按键应用中必须有电容,参数为100nF。加电容的作用是在系统受到强干扰时,稳定复位脚的电平状态。

注意:该引脚内部有一个50KΩ左右的上拉电阻,低电平会使复位生效,为避免电路异常,该电容容值请不要随意更改!

复位电路¶

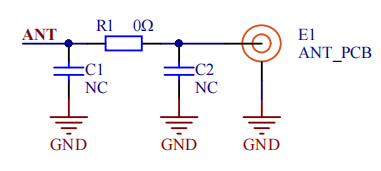

2.5 天线匹配¶

由于芯片内部已做射频前端匹配电路,所以此处预留射频前端匹配网络电路,其中C1、C2、R1预留元件位置,C1、C2为预留电容默认不焊接,R1为0Ω电阻。若因PCB设计不合理导致射频前端失配,那么可以通过C1、C2、R1组成匹配网络进行阻抗调整。

天线匹配示意图¶

3 PCB设计建议¶

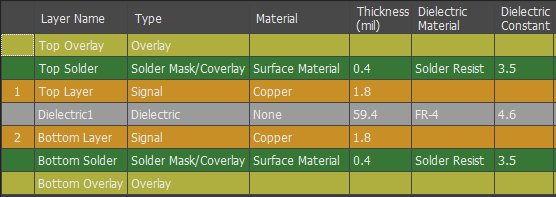

3.1 制板工艺¶

本文主要针对二层板并且单面贴设计,叠层如下图所示。 PCB厚度需根据实际情况和阻抗要求适当调整。

制板工艺说明¶

*线宽推荐如下:

板材属性 |

参数 |

|---|---|

PCB板材 |

FR4 |

PCB板厚 |

1.6mm |

50欧姆RF线宽 |

20mil |

接地铺铜与RF走线间距 |

5mil |

3.2 PCB布局¶

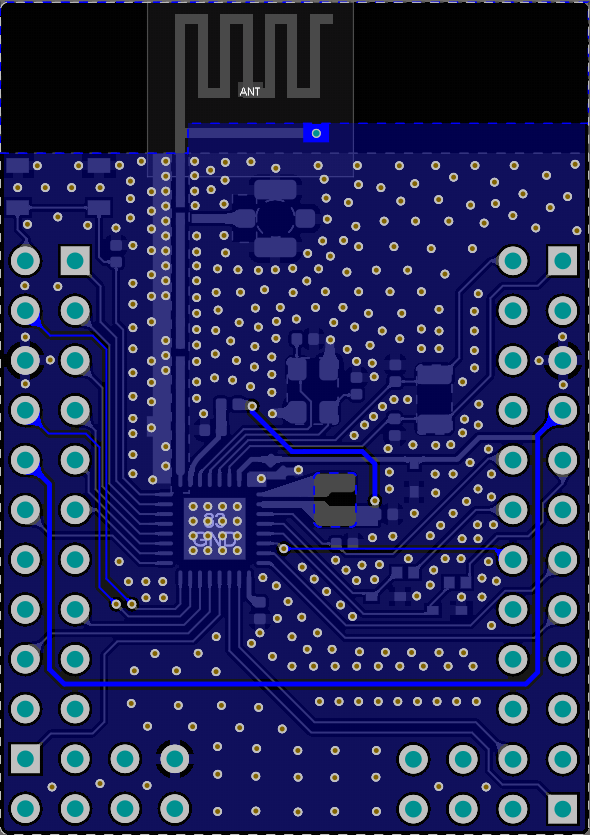

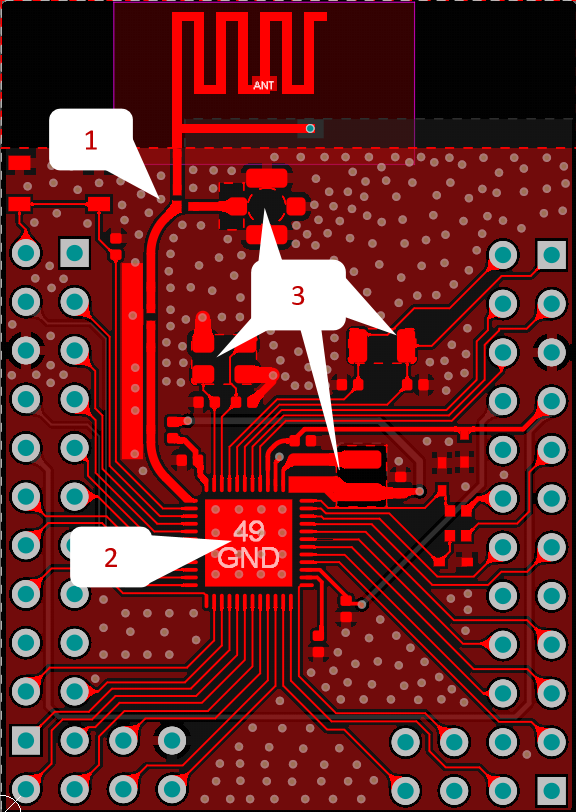

3.3 射频走线注意事项¶

晶振尽量靠近芯片引脚摆放,距离芯片越近性能相对会更好;

射频匹配链路按照50Ω走线,可以参考TOP和BOTTOM层的GND平面,RF走线尽可能短,RF线与焊盘宽度一致,天线的π型匹配并联元件焊盘和走线重合为佳;

RF线有完整的参考地,从IC端出来就进行包地处理,两边打GND过孔,底层地平面尽量宽,如标签1所指信号走线;

IPEX-1代天线端子信号引脚挖空,周围包地,尽量减小寄生电容导致阻抗突变,如标签3;

芯片底部多打过孔,QFN封装则打在E-PAD上,如标签2;

晶振应远离天线,TOP层挖空,周围包地,降低对电源和RF的干扰,需要挖空的部分如标签3;

天线辐射区域尽量不要摆放金属器件,净空区铺铜全部挖空。

射频链路走线参考如下:

射频链路走线示意图¶

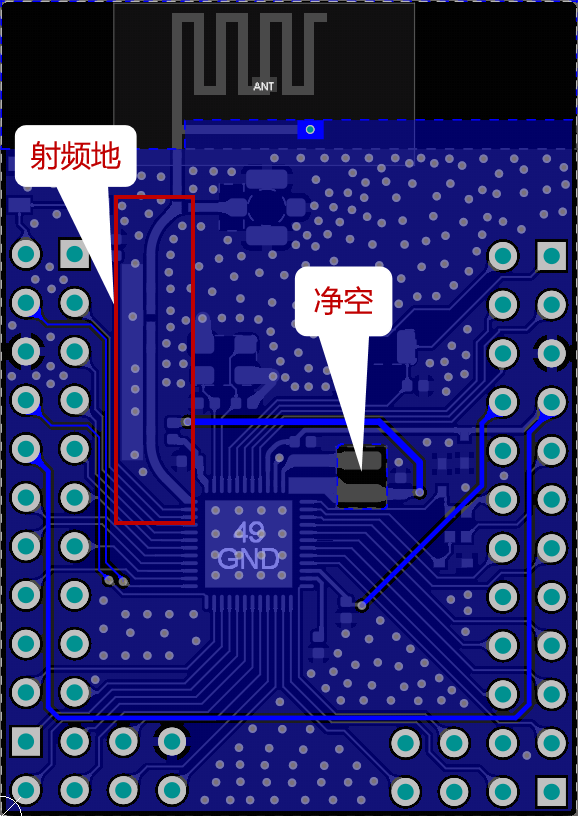

天线匹配链路底层不走线,保证地回路到芯片最短。天线匹配链路的地和芯片EPAD 是一块完整连续的地。

芯片底层不要走线;

射频地线走线如下:

射频地线走线示意图¶

4 板载天线¶

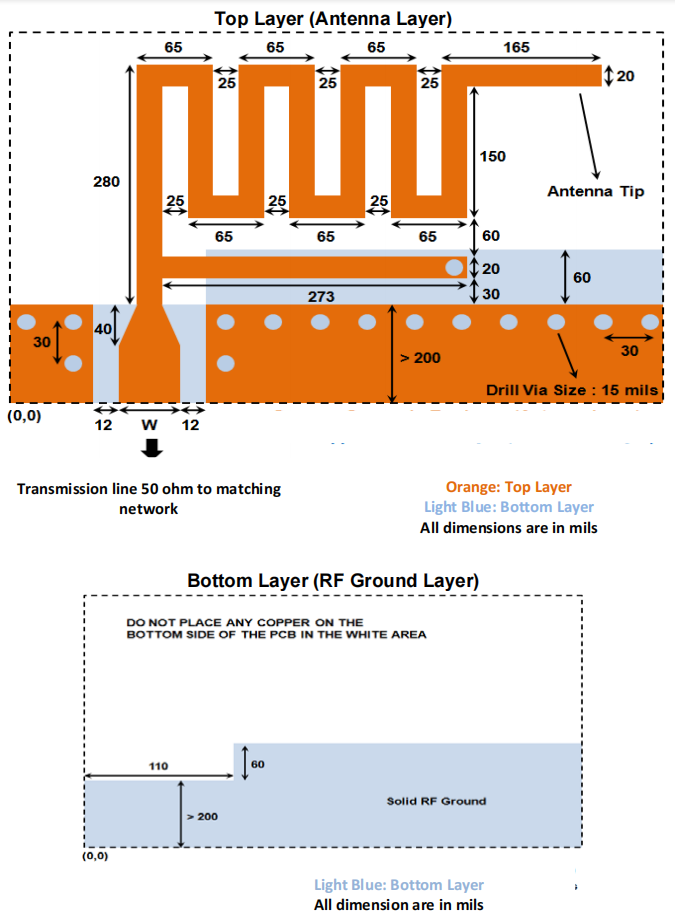

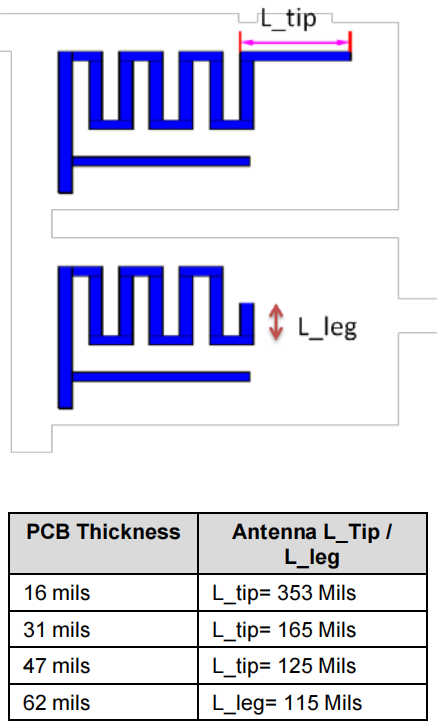

PCB Layout参考中MIFA天线尺寸如图所示。

天线设计尺寸参考

天线设计尺寸参考示意图¶

天线设计匹配参考示意图¶

注意:为保证射频性能最佳,建议由我司工程师进行样板射频参数校调!

5 BOM¶

最小系统BOM参考下表,所有PAN108x系列通用

品种 |

参数 |

型号 |

品牌 |

立创编号 |

位号 |

封装 |

数量 |

|---|---|---|---|---|---|---|---|

贴片陶瓷电容 |

4.7uF |

0402X475M6R3NT |

广东风华高新科技股份有限公司 |

C168172 |

C8, C9, C10, C11,C14 |

0402_C |

4 |

贴片陶瓷电容 |

100nF |

0402B104K160NT |

广东风华高新科技股份有限公司 |

C41851 |

C7 |

0402_C |

1 |

贴片陶瓷电容 |

18pF |

0402CG180J500NT |

广东风华高新科技股份有限公司 |

C48936 |

C3, C4, C5, C6 |

0402_C |

4 |

贴片陶瓷电容 |

NC |

\ |

\ |

\ |

C1, C2, C12, C13 |

0402_C |

4 |

贴片按键 |

4P-4.2mm x 3.25mm |

K2-1808SN-A4SW-01 |

韩荣电子有限公司 |

C92589 |

K1 |

SW-SMD(4.2x3.25x2.5) |

1 |

贴片连接器 |

IPEX-1 |

HC-RF-IPEX0303-01 |

深圳市华灿天禄电子有限公司 |

C2894919 |

E2 |

IPEX-1 |

1 |

贴片功率电感 |

2.2uH |

PIM252010-2R2MTS00 |

广东风华高新科技股份有限公司 |

C2986792 |

L1 |

SMD-2520-1.0 |

1 |

直插连接器 |

Header 2x4,2.54mm |

PH-00530 |

深圳市连盛精密连接器有限公司 |

C2685166 |

P3, P4 |

Header 2x4 |

2 |

直插连接器 |

Header 2x10,2.54mm |

PZ254V-12-20P |

XFCN(台湾兴飞) |

C492427 |

P1, P2 |

Header 2x10 |

2 |

贴片电阻 |

3.3Ω 1% |

RC-02U3R30FT |

广东风华高新科技股份有限公司 |

C321181 |

R2 |

0402_R |

1 |

贴片电阻 |

0Ω 1% |

RC-02000FT |

广东风华高新科技股份有限公司 |

C140225 |

R1、R3 |

0402_R |

2 |

贴片电阻 |

22Ω ±1% 62.5mW |

RC-02W22R0FT |

广东风华高新科技股份有限公司 |

C140225 |

R4、R5 |

0402_R |

2 |

贴片4脚晶振 |

32MHz 10ppm 12pF |

X322532MOB4SI |

深圳扬兴科技有限公司 |

C9009 |

Y1 |

SMD-3225_4P |

1 |

贴片2脚晶振 |

32.768KHz 12.5pF |

X321532768KGD2SI |

深圳扬兴科技有限公司 |

C620155 |

Y2 |

SMD-3215_2P FC - 135 |

1 |

静电放电(ESD)保护器件 |

5V |

BTRD04A035 |

Leiditech(雷卯电子) |

C5128428 |

D1 |

0402_C_RF |

1 |

瞬态抑制二极管(TVS) |

3.3V |

ESD5Z3V3 |

TC(德昌) |

C129213 |

D2、D3、D4 |

SOD-523 |

3 |

贴片IC |

PAN1080LB5A |

\ |

上海磐启微电子有限公司 |

\ |

U1 |

LQFP64-7x7-0.4 |

1 |

6 RF基本性能¶

开发板蓝牙性能¶

编号 |

Frequency(MHz) |

EVM(%) |

Carr ofst(KHz) |

Dev(KHz) |

|---|---|---|---|---|

PAN1080UB1A |

2402 |

5.5% |

-11.9 |

274 |

PAN1080UB1A |

2442 |

4.3% |

-11.5 |

265 |

PAN1080UB1A |

2472 |

6.4% |

-10.9 |

276 |

PAN1080UA3A |

2402 |

6.3% |

-12.1 |

273 |

PAN1080UA3A |

2442 |

4.7% |

-12.5 |

269 |

PAN1080UA3A |

2472 |

6.5% |

-12.8 |

275 |

PAN1080LB5A |

2402 |

7.4% |

-10.1 |

277 |

PAN1080LB5A |

2442 |

5.3% |

-10.3 |

271 |

PAN1080LB5A |

2472 |

8.5% |

-10.4 |

281 |

测试条件:

Clock |

DPLL:64M |

PSA |

E4445A |

Data rate |

1Mbps |

Payload |

37Byte |

Format |

PRBS9 |

SW |

RF_TEST |

Power set |

4dbm |