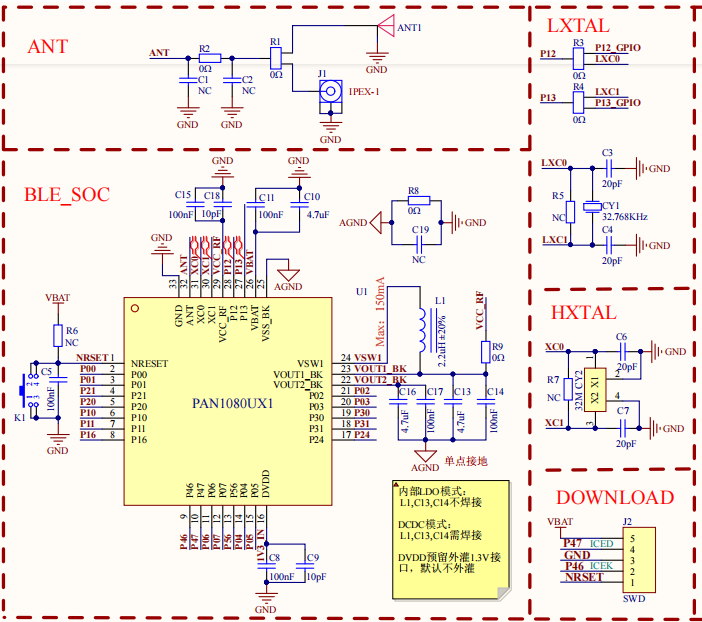

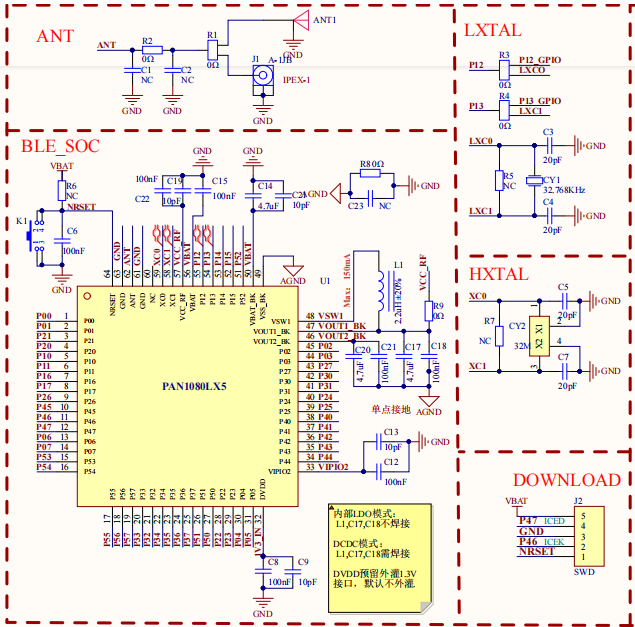

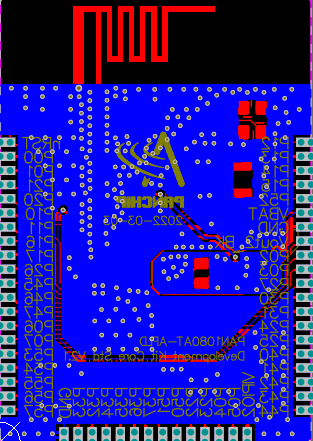

PAN1080 硬件参考设计¶

1 概述¶

本文档主要介绍 PAN1080UX1/PAN1080LX5芯片方案的硬件原理图设计、PCB 设计建议、天线设计。本文档提供 PAN1080UX1/PAN1080LX5 芯片的硬件设计方法。

2 原理图设计建议¶

2.3 电源¶

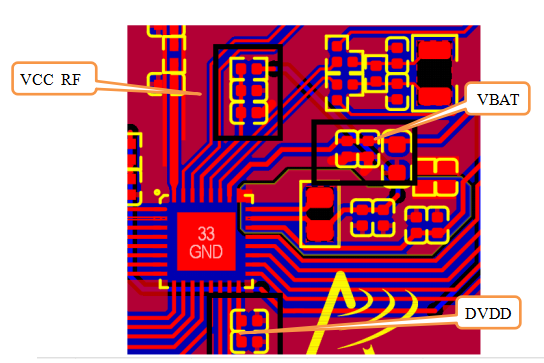

VBAT 为芯片电源脚,,要求供电能力不小于60mA,供电范围为1.8V–3.6V 。

VCC_RF、VBAT、VOUT2_B、KVOUT2_BK 至少预留两个电容,靠近芯片管脚。

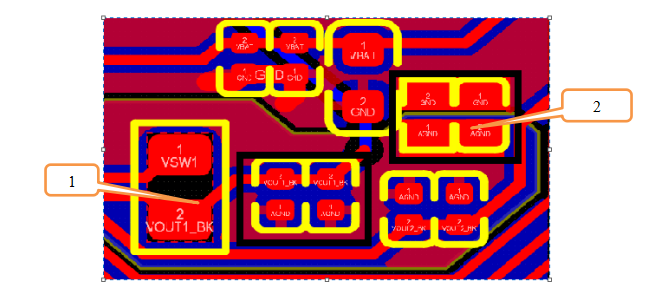

2.4 DCDC¶

DCDC 电路外围为L1、C13、C14。要求L1 DCR小于80mΩ,峰值电流至少为150mA。芯片电源有两种工作模式,DCDC模式和内部LDO模式。开启DCDC 可以节省功耗。开启LDO模式后芯片内部将VBAT 连接到VOUT1_BK,这时VOUT1_BK 处的一个电感和两个电容可以不焊接。

2.5 DVDD¶

DVDD需要预留外灌1.3V接口,且外挂100nF和10pF电容。1.3V外灌默认不焊接,是否外灌和软件应用运行功耗有关。 如果外灌则要求供电压1.3V,驱动电流大于20mA,纹波小于2%。外挂电容不超过1uF,否则会影响芯片正常启动。

2.6 VIPIO2¶

VIPIO2电源脚在LQFP64 封装上有独立的PIN 脚。 因此PAN1080LX5 可配置两组不同的IO输出电平。P40、P41、P42、P43、,P44的输出电平等于电源VIPIO2的供电电压。VIPIO输入电压范围为1.8V–VBAT。 其余IO的输出电平等于VBAT供电电压。

VIPIO2电源脚在QFN32 封装上和VBAT脚绑定在一起。因此PAN1080UX1 IO输出电平等于VBAT。

2.7 32M晶振¶

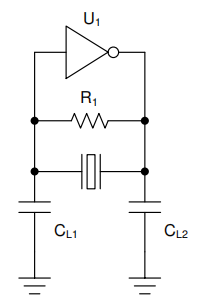

32MHz晶振外围电路示意图¶

上图这种振荡器,晶体和负载电容器构成 π 型滤波器,为内部放大器提供 180° 相移,同时使振荡器一直锁定在指定的频率。为了使该频率正确,必须根据晶体的容性负载 (CL) 参数正确地确定负载电容的尺寸。可以通过相对于晶体的所需负载电容 CL 正确确定负载电容器的尺寸来设置 32MHz 晶体振荡器的频率。从晶体的角度而言,两个电容器串联放置,这意味着必须使用用于计算最终总电容的“电阻器并联”方程。还要注意 PCB迹线和焊盘会增加一些寄生电容。可以通以下公式 来计算正确的负载电容值。

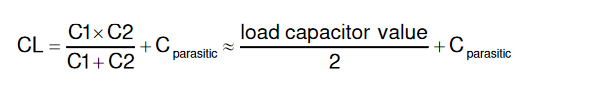

负载电容计算公式¶

最后的简化要求 C1 和 C2 相等, Cparasitic =5pF 。

上图中C1、C2为高速晶振的负载电容。其参数将影响晶振频率,负载电容的选择请参考所选晶振的规格书。

晶振推荐如下:

1) 晶体频率132MHz;

2) ESR小于等于60ohm;

3) 晶体负载电容小于等于20pF;

4) 晶体频率精度高于±20ppm;

晶振封装形式

晶振负载电容/pF

焊接电容值/pF

3225

9

10

12

12

20

30

圆柱

9

10

12

12

20

30

49S

9

10

12

15

20

30

2.8 32K晶振¶

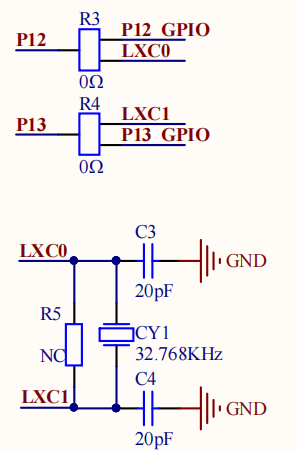

32KHz晶振外围电路原理图¶

低速晶振电路支持外部32.768KHz无源晶振。C3、C4为低速晶振的负载电容;低速晶振推荐用户选择ESR<80KΩ的晶振。

由于部分用户需要使用外部32K的芯片管脚复用为IO使用,所以做以下电路进行预留接口。通过两个0欧姆电阻将P1.2、P1.3复用为晶振接口和普通IO。

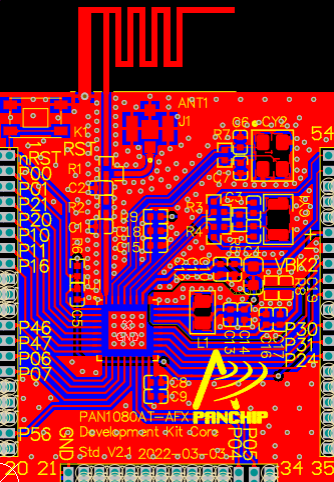

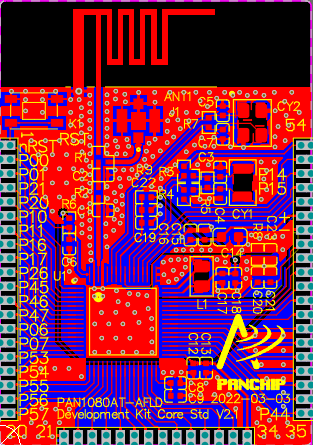

3 PCB设计建议¶

3.1 制版工艺¶

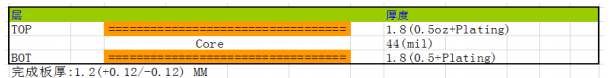

本Guide主要针对二层板并且单面贴设计,叠层如下图所示。 PCB具体厚度根据实际情况和阻抗要求适当调整。

制版工艺说明¶

*线宽推荐如下:

板材属性 |

参数 |

|---|---|

PCB板材 |

FR4 |

PCB板厚 |

1.2mm |

50欧姆RF线宽 |

20mil |

接地铺铜与RF走线间距 |

5.1mil |

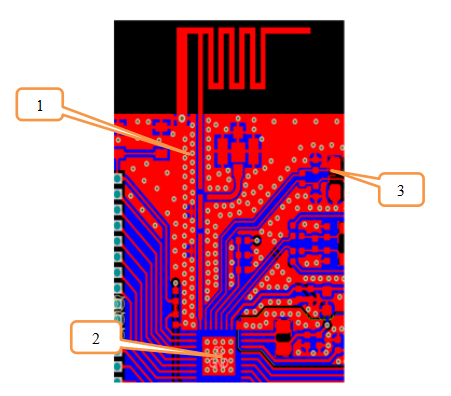

3.6 射频走线注意事项¶

射频匹配链路按照50Ω走线,可以参考TOP和BOT层的GND平面,RF线与焊盘宽度一致,阻

抗没有突变。

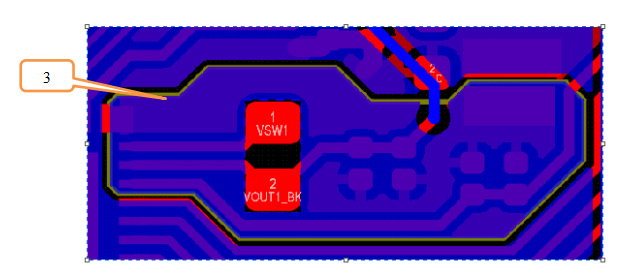

RF线有完整的参考地,从IC端出来就进行包地处理,两边均匀的打GND过孔,底层到芯片底部地平面尽量宽,如标签1;

芯片EPAD多打过孔,如标签2;

晶振要远离天线和天线匹配链路,晶振走线和其他走线垂直布线,减少晶振对RF的干扰,如标签3;

晶振线两边包地,以降低对电源和RF的干扰

天线辐射区域尽量保证没有金属器件。

天线的Pi型匹配电路要走顺,并联元件焊盘和走线重合为好。

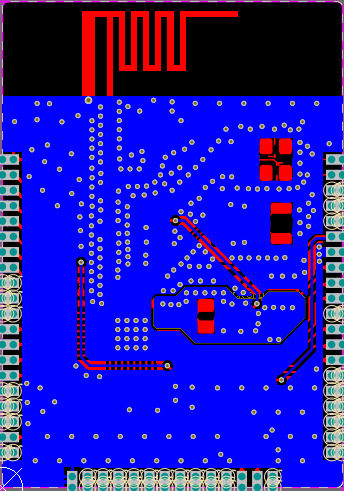

射频链路走线参考如下:

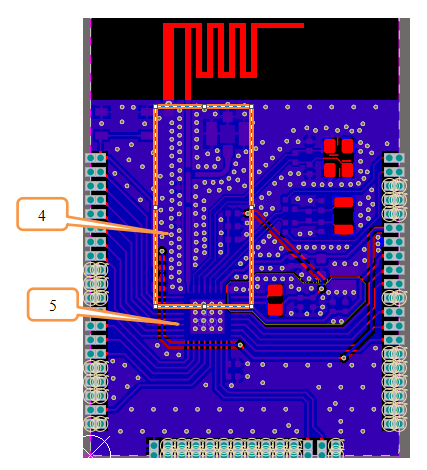

射频链路走线示意图¶

天线匹配链路底层不走线,天保证线地回路到芯片最短。天线匹配链路的地和芯片EPAD 是一块完整平滑的地。如标签4,橙色方框;

芯片底层不要走线,如标签5;

射频地线走线如下:

射频地线走线示意图¶