量产烧录¶

1 芯片烧录口硬件连接¶

对于遵循 PAN10xx 硬件参考设计 文档规范的方案硬件板,可支持通过 SWD 接口烧录程序。

a)芯片支持通过 JLink 或 Panlink 两种方式进行烧录,其接线方式分别如表1-1、表1-2所示。

JLink |

连接 |

PAN107x/PAN101x SoC |

|---|---|---|

VTref 3.3V |

<—> |

VBAT |

GND |

<—> |

GND |

SWDIO |

<—> |

P01 |

SWDCLK |

<—> |

P00 |

Panlink 2.0 |

连接 |

PAN107x/PAN101x SoC |

|---|---|---|

VDD |

<—> |

VBAT |

GND |

<—> |

GND |

A2 |

<—> |

RST |

A3 |

<—> |

P01 |

A4 |

<—> |

P00 |

b)若需要烧录无任何外围器件的裸芯片,则 PAN107x/PAN101x SoC 烧录接线方式如表1-3、表1-4所示。

JLink |

连接 |

PAN107x/PAN101x 裸芯片 |

|---|---|---|

VTref 3.3V |

<—> |

VCC_RF |

GND |

<—> |

GND 或 ePAD |

SWDIO |

<—> |

P01 |

SWDCLK |

<—> |

P00 |

Panlink 2.0 |

连接 |

PAN107x/PAN101x 裸芯片 |

|---|---|---|

VDD |

<—> |

VCC_RF |

GND |

<—> |

GND 或 ePAD |

A2 |

<—> |

RST |

A3 |

<—> |

P01 |

A4 |

<—> |

P00 |

提醒:关于裸芯片烧录,根据不同封装的电源/地引脚类型,在满足上述表1-3/表1-4接线要求的前提下,为提高烧录成功率有如下建议:

对于有 VBAT 电源引脚的封装,烧录的时候建议将芯片 VBAT 通过跳线与芯片 VCCRF 引脚接在一起

对于有 DVSS 地引脚的封装,烧录的时候建议将芯片 DVSS 通过跳线与芯片 GND 或 ePAD 引脚接在一起

注意以上接线建议仅针对裸片烧录的场景,在有外围器件的正常工作场景中,电源和地的接线应按照 PAN10xx 硬件参考设计 文档中的规范进行设计。

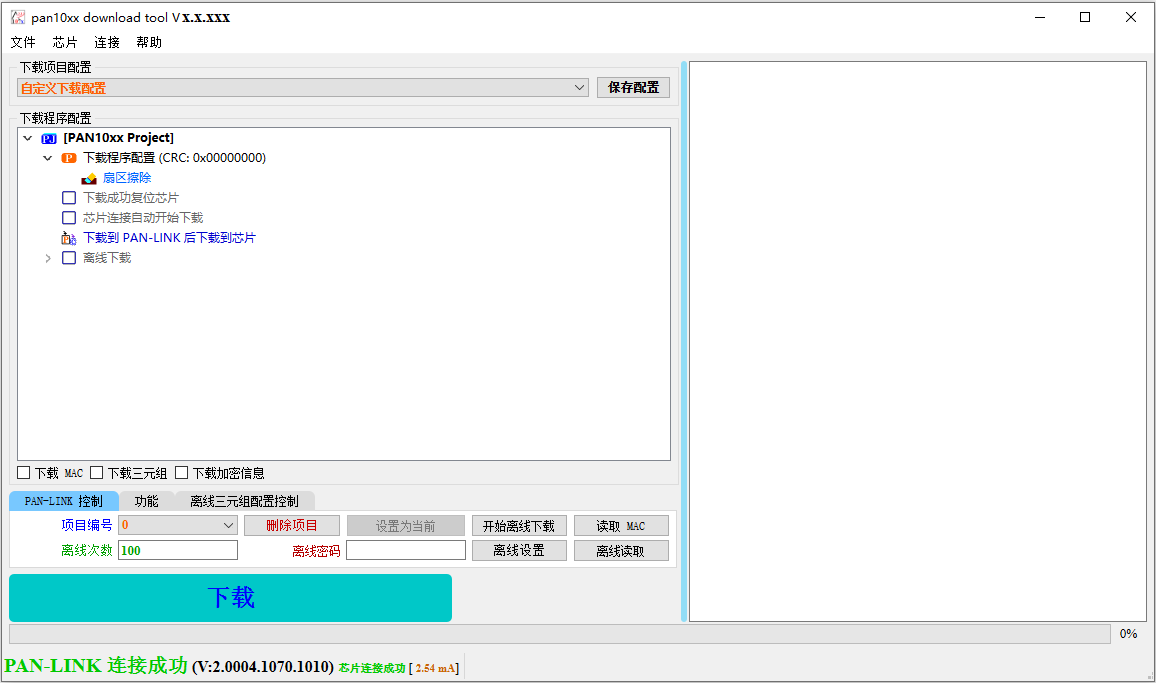

2 量产烧录工具¶

为配合 Panlink 2.0 烧录器进行量产烧录,我们提供了对应的 PC 上位机工具。

下载

2.1 硬件准备¶

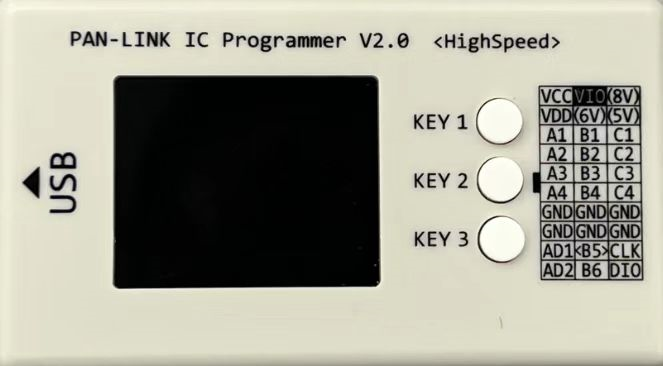

预先将 Panlink 2.0 通过 MiniUSB 线连接到 PC 电脑。

图2-1 Panlink 2.0 烧录器¶

图2-2 MiniUSB 连接线¶

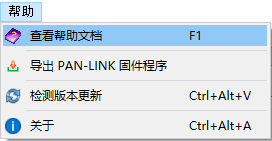

如果 Panlink 2.0 固件程序不支持 PAN107x 芯片烧录,则需要根据提示自动更新升级。

或按照帮助文档方法更新 Panlink 2.0 固件程序。

2.1.1 PAN107x/PAN101x 芯片烧录接线¶

注: Panlink 2.0 接口的 VCC 与 VIO通过跳线帽短接。

Panlink 2.0 接口脚 |

连接 |

PAN107x/PAN101x 芯片脚 |

|---|---|---|

VDD |

<—> |

VDD |

GND |

<—> |

GND |

A1 |

<—> |

RST |

A3 |

<—> |

P01 |

A4 |

<—> |

P00 |