GPIO Open-Drain Output¶

1 功能概述¶

本例程演示如何使用 GPIO HAL Driver 实现 GPIO 开漏(Open-Drain)输出功能。

2 环境准备¶

硬件设备与线材:

PAN107X EVB 核心板与底板各一块

JLink 仿真器(用于烧录例程程序)

USB-TypeC 线一条(用于底板供电和查看串口打印 Log)

杜邦线数根或跳线帽数个(用于连接各个硬件设备)

硬件接线:

将 EVB 核心板插到底板上

使用 USB-TypeC 线,将 PC USB 插口与 EVB 底板 USB->UART 插口相连

使用杜邦线将 EVB 底板上的 TX 引脚接至核心板 P16,RX 引脚接至核心板 P17

使用杜邦线将 EVB 底板上的 LED3 排针与 P10 排针相连

使用杜邦线将 JLink 仿真器的:

SWD_CLK 引脚与 EVB 底板的 P00 排针相连

SWD_DAT 引脚与 EVB 底板的 P01 排针相连

SWD_GND 引脚与 EVB 底板的 GND 排针相连

PC 软件:

串口调试助手(UartAssist)或终端工具(SecureCRT),波特率 921600(用于接收串口打印 Log)

3 编译和烧录¶

例程位置:<PAN10XX-NDK>\01_SDK\nimble\samples\peripheral\gpio_output_open_drain\keil_107x

双击 Keil Project 文件打开工程进行编译烧录。

4 例程演示说明¶

烧录完成后,芯片会通过串口打印初始化 Log:

Try to load HW calibration data.. DONE. - Chip Info : 0x1 - Chip CP Version : 255 - Chip FT Version : 6 - Chip MAC Address : E11000000FF8 - Chip UID : 6D0001465454455354 - Chip Flash UID : 4250315A3538380B005B7B4356037D78 - Chip Flash Size : 512 KB

观察 EVB 底板上的发光二极管 LED3,可以看到其以 1Hz 的频率闪烁

注:此模式下灯光亮度较弱,这是因为 EVB 底板上的 LED3 电路被设计成高电平驱动亮灯,而由于 GPIO 开漏输出模式下配置了 SoC 内部上拉电阻(50KΩ左右),因此驱动电流较小,从而导致灯光亮度较弱。

5 开发者说明¶

5.2 GPIO HAL Driver 初始化配置说明¶

在使用 GPIO HAL Driver 的时候,是通过一个名为 HAL_GPIO_Init() 的接口对 GPIO 进行初始化配置的,此接口接受 2 个参数:

pinID:待配置的 GPIO 引脚initStruct:初始化结构体参数,其结构体成员有 3 个:mode:GPIO 工作模式,具体分为 5 种:模拟输入、数字输入、推挽输出、开漏输出、准双向pull:内部上拉/下拉电阻使能,可选择使能内部上拉电阻、使能内部下拉电阻、或不使能内部上下拉电阻level:指定 GPIO 初始化电平(仅当 GPIO 被配置为输出功能时有效)

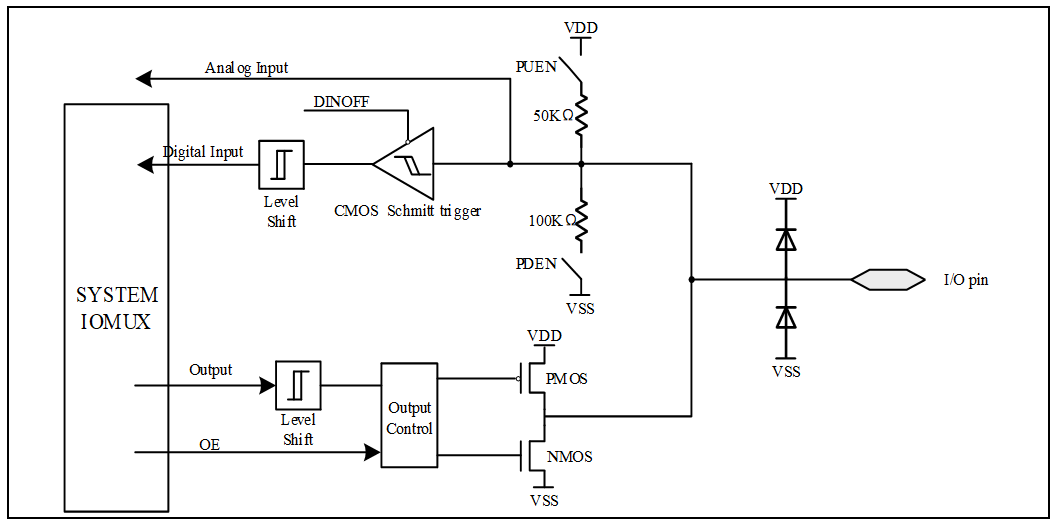

GPIO 软件配置与 GPIO 模块框图中的内部信号对应关系如下:

当

mode参数被配置为模拟输入(HAL_GPIO_MODE_INPUT_ANALOG)时:DINOFF = 1(关闭 Digital Input 通路)

OE = 0(关闭输出通路使能,即 PMOS 与 NMOS 均不导通)

注:此状态下 I/O pin 上的电平将只会通过 Analog Input 通路传入芯片内部,对于芯片大部分引脚来说,此时 IO 相当于浮空/高阻状态;对于某些支持模拟输入功能的引脚,如 P04 (ADC_CH0),则当 ADC 模块的通道 0 使能后,ADC 通过 GPIO 的 Analog Input 通路检测外部 IO 的电压信号

当

mode参数被配置为数字输入(HAL_GPIO_MODE_INPUT_DIGITAL)时:DINOFF = 0(打开 Digital Input 通路)

OE = 0(关闭输出通路使能,即 PMOS 与 NMOS 均不导通)

注:此状态下 I/O pin 上的电平将可以通过 Digital Input 通路传入芯片内部,对于芯片中带有输入功能的数字模块(如 GPIO 模块的外部输入检测、UART 模块 的 Rx 信号线、I2C 模块的 CLK/SDA 信号线等),均需开启对应 IO 的 Digital Input 数字输入通路方可正常使用

当

mode参数被配置为推挽输出(HAL_GPIO_MODE_OUTPUT_PUSHPULL)时:DINOFF = 1(关闭 Digital Input 通路)

OE = 1(打开输出通路使能)

若 Output = 1,则 PMOS 导通,NMOS 不导通,I/O pin 为高电平(VDD)

若 Output = 0,则 PMOS 不导通,NMOS 导通,I/O pin 为低电平(VSS)

当

mode参数被配置为开漏输出(HAL_GPIO_MODE_OUTPUT_OPENDRAIN)时:DINOFF = 1(关闭 Digital Input 通路)

OE = 1(打开输出通路使能,PMOS 强制不导通,I/O pin 需要通过内部或外部上拉电阻将其拉为高电平)

若 Output = 1,则 NMOS 不导通,I/O pin 被上拉电阻拉成高电平(VDD)

若 Output = 0,则 NMOS 导通,I/O pin 为低电平(VSS)

当

mode参数被配置为准双向(HAL_GPIO_MODE_QUASI_BIDIRECTIONAL)时:DINOFF = 0(打开 Digital Input 通路)

OE = 1(打开输出通路使能,PMOS 强制不导通,I/O pin 需要通过内部或外部上拉电阻将其拉为高电平)

若 Output = 1,则 NMOS 不导通,I/O pin 被上拉电阻拉成高电平(VDD)

若 Output = 0,则 NMOS 导通,I/O pin 为低电平(VSS)

注:此状态下 I/O pin 可被看做准双向口:作为输出使用的时候,直接配置 Output = 1/0 既可输出高/低电平,此时输出行为类似开漏输出;作为输入使用的时候,需要先配置 Output = 1(以确保 NMOS 不导通),然后 I/O pin 的高低电平状态既可正常通过 Digital Input 通路传入芯片内部

当

pull参数被配置为上拉(HAL_GPIO_PULL_UP)时:PUEN = 1(打开内部上拉电阻通路)

PDEN = 0(关闭内部下拉电阻通路)

当

pull参数被配置为下拉(HAL_GPIO_PULL_DOWN)时:PUEN = 0(关闭内部上拉电阻通路)

PDEN = 1(打开内部下拉电阻通路)

当

pull参数被配置为禁用上下拉(HAL_GPIO_PULL_DISABLE)时:PUEN = 0(关闭内部上拉电阻通路)

PDEN = 0(关闭内部下拉电阻通路)

当

level参数被配置为高电平(HAL_GPIO_LEVEL_HIGH)时:Output = 1(初始化输出高电平,仅在输出模式下生效)

当

level参数被配置为低电平(HAL_GPIO_LEVEL_LOW)时:Output = 0(初始化输出低电平,仅在输出模式下生效)

PAN10xx SoC 各个 IO 上电默认状态:

P00 为 SWD CLK 功能,且 IO 内部上拉电阻开启

P01 为 SWD DATA 功能,且 IO 内部上拉电阻开启

除 P00/P01 以外的所有其他 IO,均为 GPIO 功能(模拟输入模式),且内部上下拉电阻关闭